## Chapter 4 Microchip PIC18 Architecture

#### Market shares of silicon manufacturers and MCU suppliers in 2021.

#### 2Q21 Top 10 Semiconductor Sales Leaders (\$M, Including Foundries)

| 2Q21<br>Rank | 1Q21<br>Rank | Company           | Headquarters | 1Q21<br>Total IC | 1Q21<br>Total<br>O-S-D | 1Q21<br>Total<br>Semi | 2Q21<br>Total IC | 2Q21<br>Total<br>O-S-D | 2Q21<br>Total Semi | 2Q21/1Q21<br>% Change |

|--------------|--------------|-------------------|--------------|------------------|------------------------|-----------------------|------------------|------------------------|--------------------|-----------------------|

| 1            | 2            | Samsung           | South Korea  | 16,152           | 920                    | 17,072                | 19,262           | 1,035                  | 20,297             | 19%                   |

| 2            | 1            | Intel             | U.S.         | 18,676           | 0                      | 18,676                | 19,304           | 0                      | 19,304             | 3%                    |

| 3            | 3            | TSMC (1)          | Taiwan       | 12,911           | 0                      | 12,911                | 13,315           | 0                      | 13,315             | 3%                    |

| 4            | 4            | SK Hynix          | South Korea  | 7,270            | 358                    | 7,628                 | 8,762            | 451                    | 9,213              | 21%                   |

| 5            | 5            | Micron            | U.S.         | 6,629            | 0                      | 6,629                 | 7,681            | 0                      | 7,681              | 16%                   |

| 6            | 6            | Qualcomm (2)      | U.S.         | 6,281            | 0                      | 6,281                 | 6,472            | 0                      | 6,472              | 3%                    |

| 7            | 8            | Nvidia (2)        | U.S.         | 4,842            | 0                      | 4,842                 | 5,540            | 0                      | 5,540              | 14%                   |

| 8            | 7            | Broadcom Inc. (2) | U.S.         | 4,364            | 485                    | 4,849                 | 4,400            | 490                    | 4,890              | 1%                    |

| 9            | 10           | MediaTek (2)      | Taiwan       | 3,849            | 0                      | 3,849                 | 4,496            | 0                      | 4,496              | 17%                   |

| 10           | 9            | ті                | U.S.         | 3,793            | 235                    | 4,028                 | 4,030            | 269                    | 4,299              | 7%                    |

| _            |              | IOP-10 IOTa       |              | 84,767           | 1,998                  | 86,765                | 93,262           | 2,245                  | 95,507             | 10%                   |

#### Leading MCU Suppliers (\$M)

| 2021<br>Rank | Company   | Headquarters | 2020  | 2021  | 21/20<br>% Chg | 2021<br>Marketshare |  |

|--------------|-----------|--------------|-------|-------|----------------|---------------------|--|

| 1            | NXP       | Europe       | 2,980 | 3,795 | 27%            | 18.8%               |  |

| 2            | Microchip | U.S.         | 2,872 | 3,584 | 25%            | 17.8%               |  |

| 3            | Renesas   | Japan        | 2,748 | 3,420 | 24%            | 17.0%               |  |

| 4            | ST        | Europe       | 2,506 | 3,374 | 35%            | 16.7%               |  |

| 5            | Infineon  | Europe       | 1,953 | 2,378 | 22%            | 11.8%               |  |

Source: Company reports, IC Insights

(1) Foundry (2) Fabless

Source: Com any reports, IC Ins ghts' Strategic Reviews database

Design Only Manufacturing Only

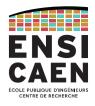

Technology used during labs

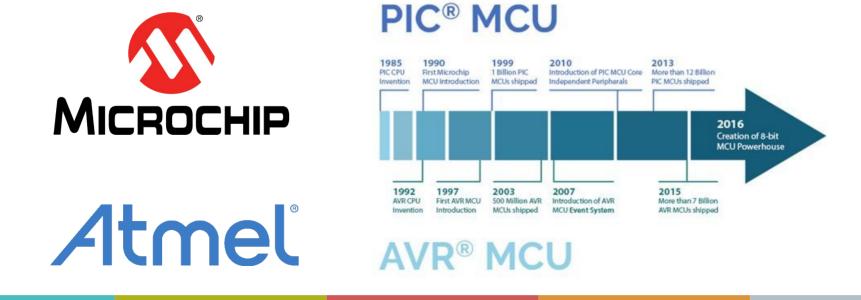

The American company Microchip is an electronic device manufacturer. Most of its turnover (fr: *chiffre d'affaires*) is due to MCUs: about 60% come from the PIC family according to Microchip ESC Filing.

In 2016 Microchip bought Atmel, its major concurrent on the 8-bit MCU market.

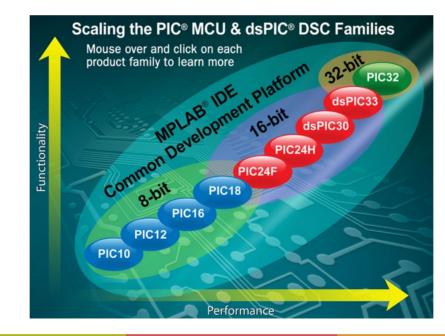

With its large range of MCU solutions, Microchip can win its clients loyalty by offering them the possibility to aim for various applications and markets.

Like many manufacturers, Microchip also supplies tools that make it easy to switch from a specific architecture to another (e.g. migration from PIC18 to PIC32).

#### 5

#### **MICROCHIP PIC18 MCUs**

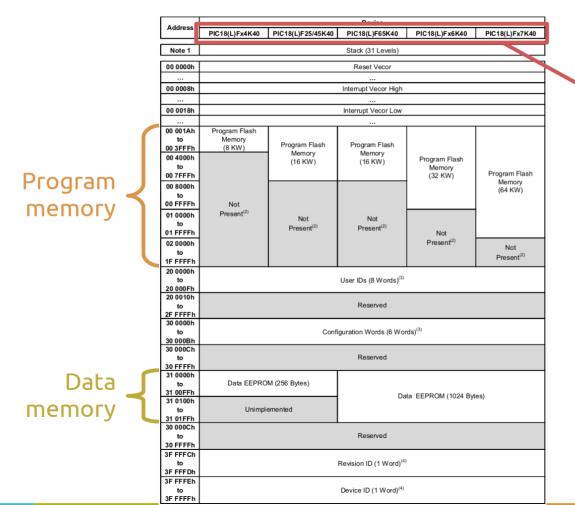

ENSI CAEN COLE PUBLIQUE D'INCÉMIEURS CENTRE DE RECHERCHE

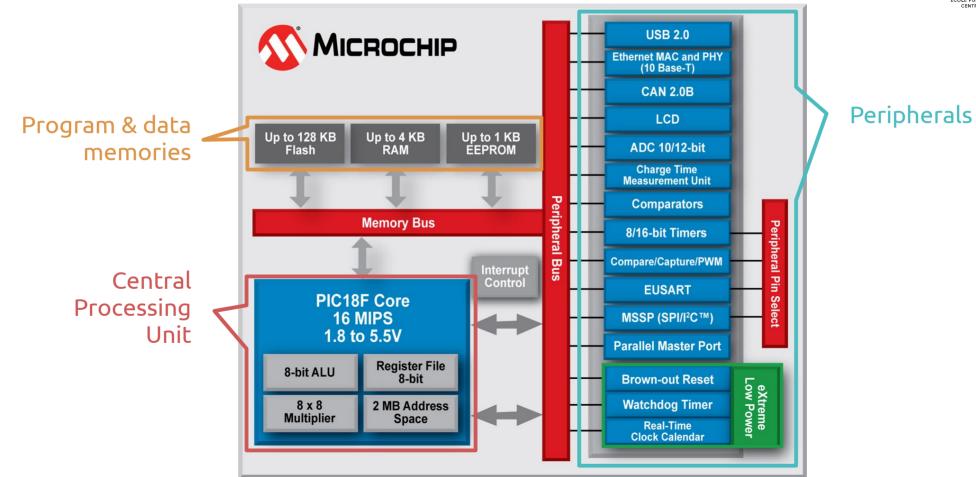

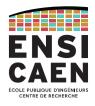

## **CENTRAL PROCESSING UNIT**

Architecture

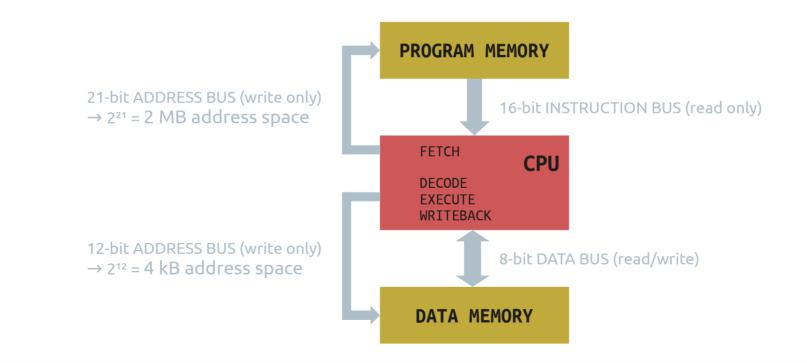

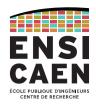

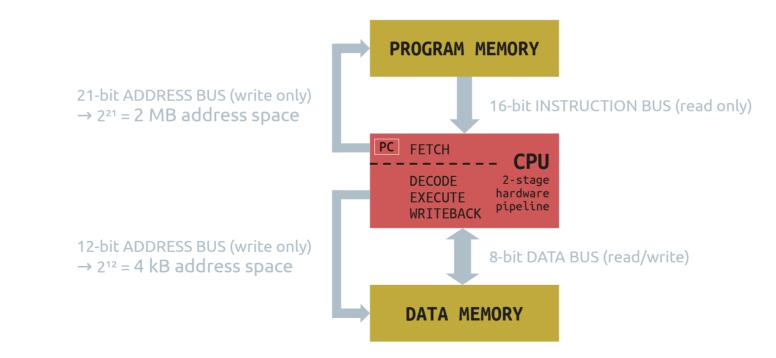

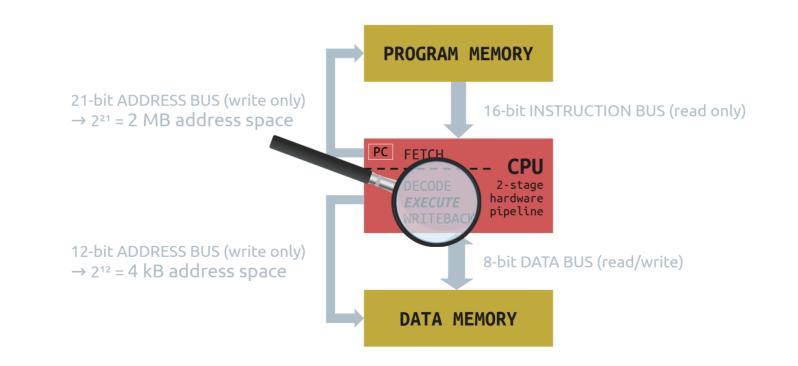

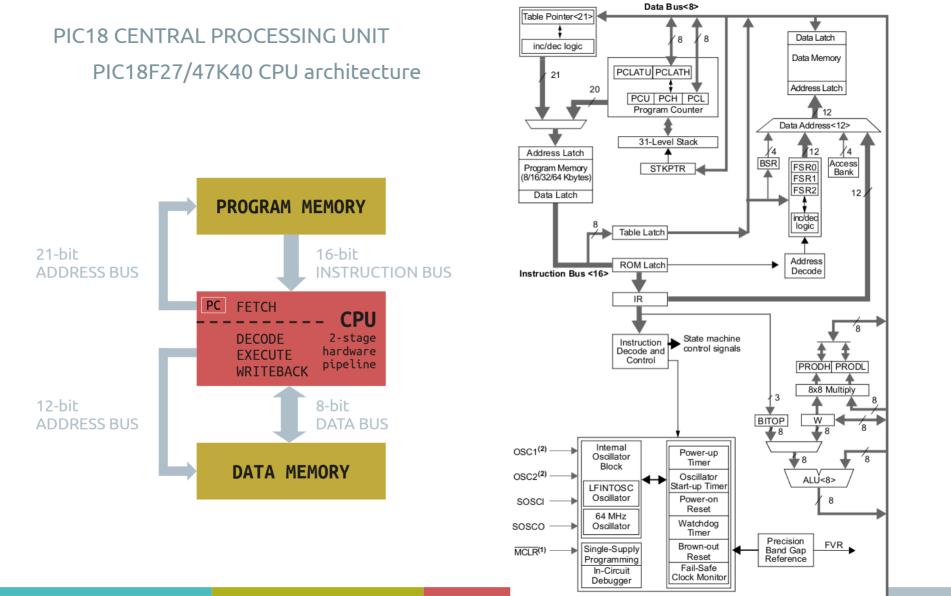

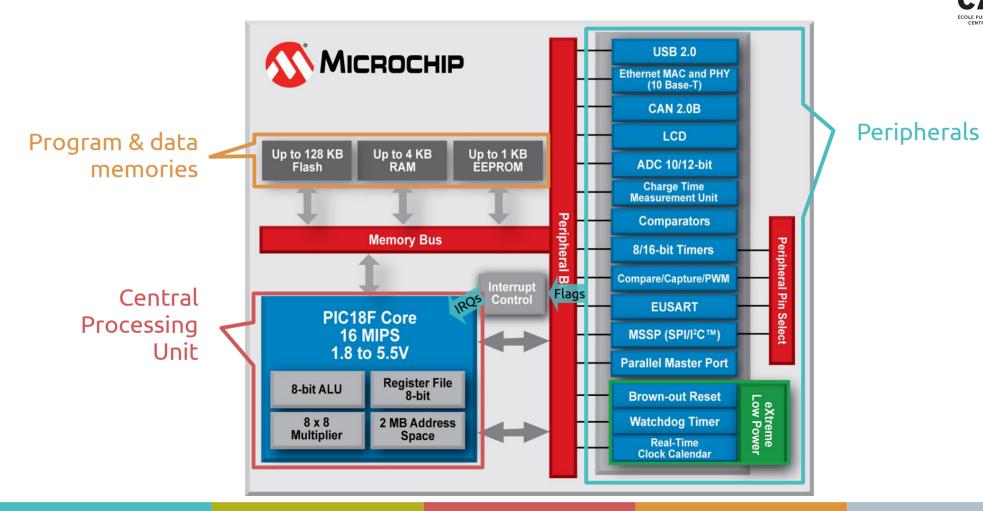

Just like the Atmel AVR, Microchip PIC18 follow a Harvard architecture: program and data memories are physically separated and their own addressing space are distinct.

Architecture

PIC18 CPUs are designed with a 2-stages hardware pipeline. They can decode-executestore an instruction while fetching the next one from the program memory.

Max performance of 16 MIPS.

Architecture

Except in sleep mode, the CPU executes a constant flow of instructions coming out of the main memory.

Some instructions ask the CPU to load or store a data from or to the data memory.

Architecture

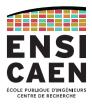

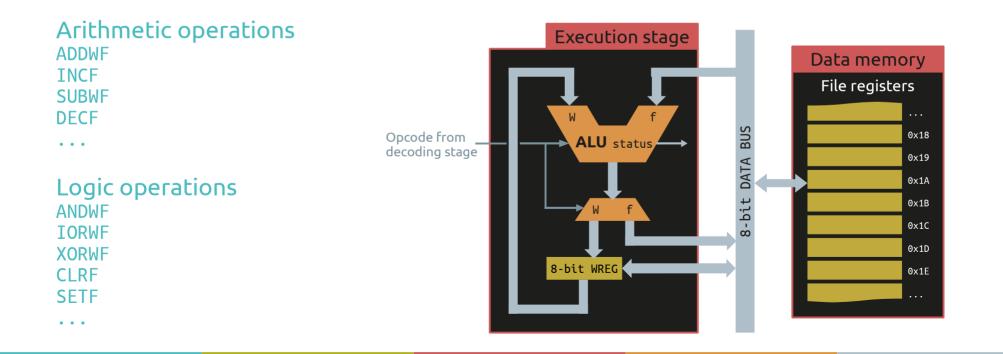

Let's dive into the EXECUTION stage to see the PIC18 Execution Units (EUs). As the PIC18 is a 8-bit MCU, the EUs can only operate on 8-bit integer values.

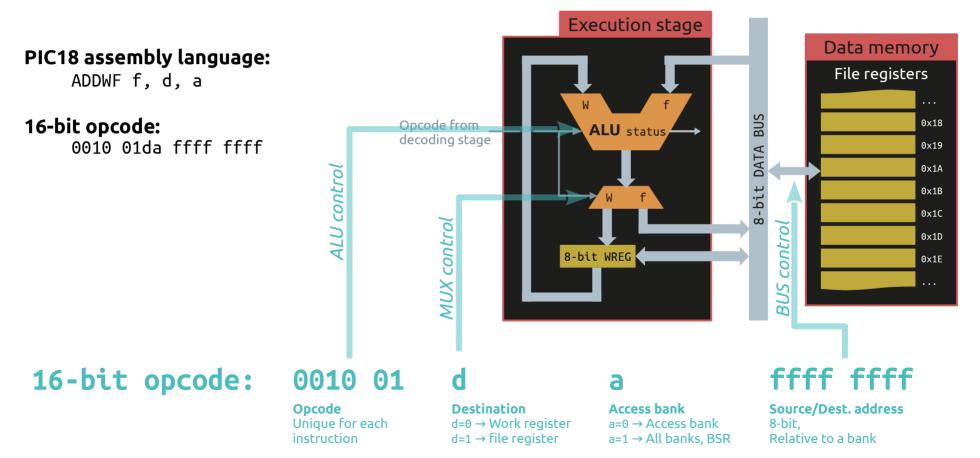

Execution Unit: ALU

The **Arithmetic and Logic Unit (ALU)** is an execution unit in charge of arithmetic (+, -) and logic (&, |, ^, !, ...) operations on 8-bit integer values.

Execution Unit: ALU

Any arithmetic or logic operation use by default a first 8-bit operand stored in the working register WREG and a second operand in the file register (data memory).

Example of an assembly language instruction and equivalent operation code (opcode).

#### Execution Unit and Decoding Unit

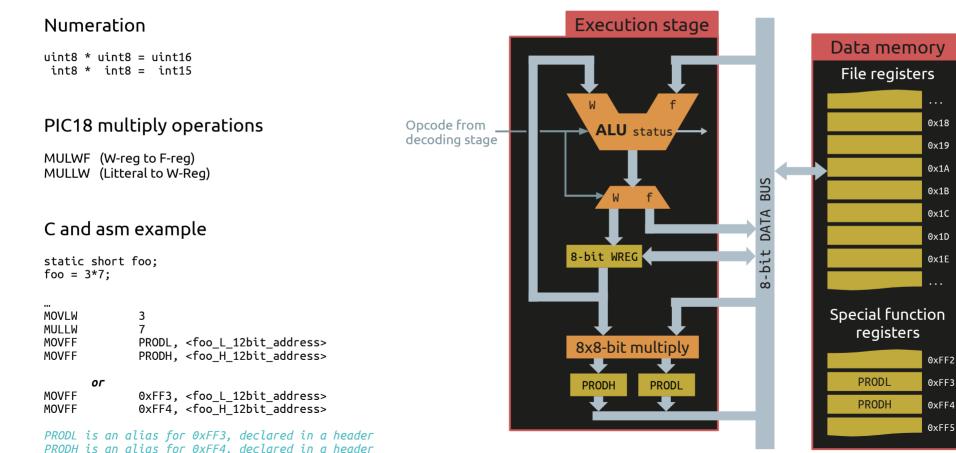

Execution Unit: 8-bit x 8-bit integer multiplication

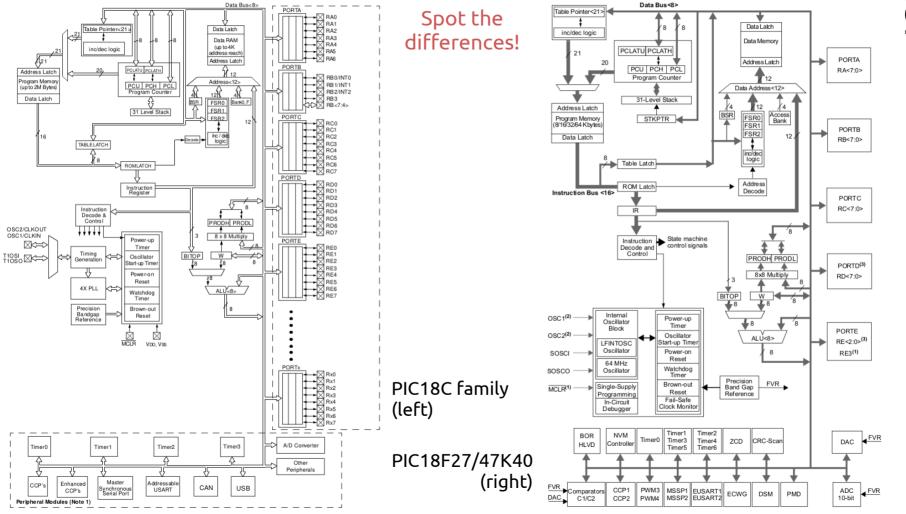

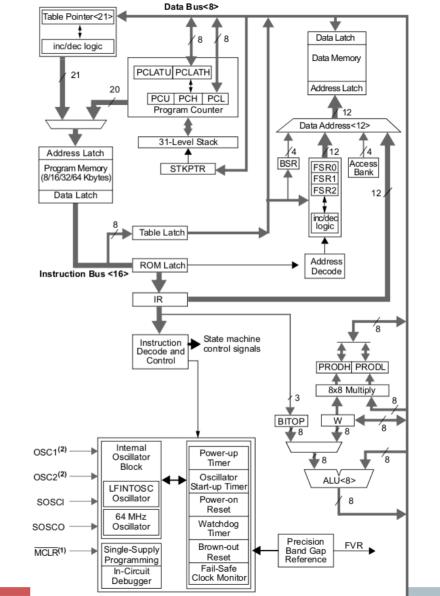

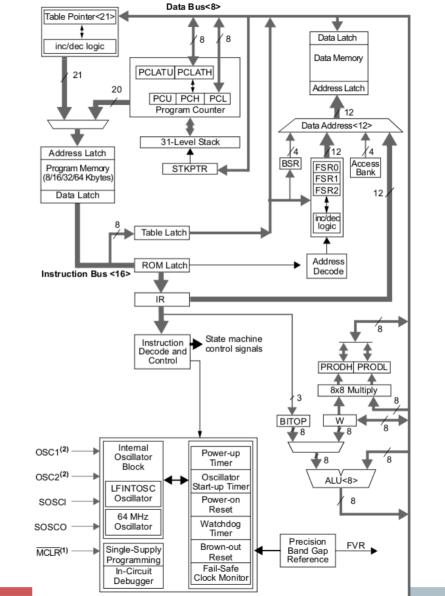

#### PIC18 architecture

#### Peripherals

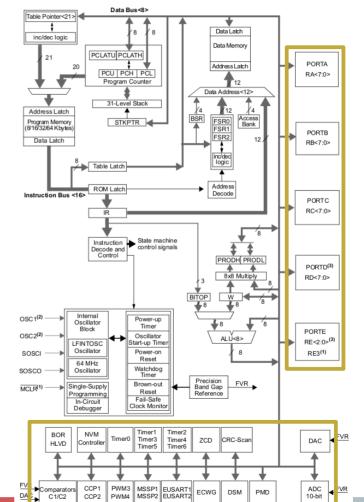

PIC18 CENTRAL PROCESSING UNIT PIC18F27/47K40 CPU architecture

Find following items in this schematic

Flash memory

RAM memory

#### Buses

program memory address bus data memory address bus data bus

#### Hardware pipeline stages

Fetch Decode Execute (ALU, multiplier) Writeback

Program Counter register

Now that you know how the PIC18 CPU is made, you shall adapt your programming habits.

This CPU (like most of low-power MCUs) does not have any Floating-Point Unit. Therefore you should avoid using floats and doubles, and use integers instead.

Also as this MCU uses an 8-bit CPU you should use 8-bit integers (char C-type) as much as possible. They are usually large enough for control applications.

Finally you saw that the ALU performs simple operations. You should then avoid using advanced operators such as '/', '%', ...

| С-Туре                          | custom typedef | Memory space                                                              | Values              |  |  |

|---------------------------------|----------------|---------------------------------------------------------------------------|---------------------|--|--|

| char                            | int8           | 8 bits / 1 byte                                                           | -128 / 127          |  |  |

| unsigned char                   | uint8          | 8 bits / 1 byte                                                           | 0 / 255             |  |  |

| short                           | int16          | 16 bits / 2 bytes                                                         | -32768 / +32767     |  |  |

| unsigned short                  | uint16         | 16 bits / 2 bytes                                                         | 0 / +65535          |  |  |

| long                            | int32          | 32 bits / 4 bytes                                                         | -2G / +2G           |  |  |

| unsigned long                   | uint32         | 32 bits / 4 bytes                                                         | 0 / +4G             |  |  |

| long long                       | int64          | 64 bits / 8 bytes                                                         | -9E / +9E           |  |  |

| unsigned long long              | uint64         | 64 bits / 8 bytes                                                         | 0 / +18E            |  |  |

| int                             |                | processor dependant                                                       | processor dependant |  |  |

| unsigned int<br>float<br>double |                | processor dependant<br>32 bits / 4 bytes (PIC/<br>32 bits / 4 bytes (PIC/ | XC8)                |  |  |

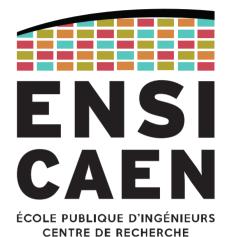

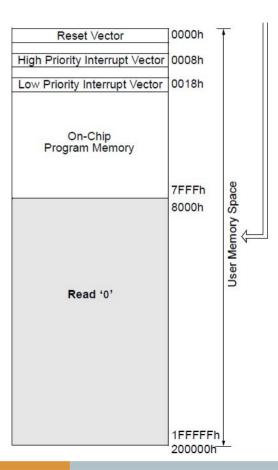

#### Program and data memory map

Size of program and data memories depends on the device

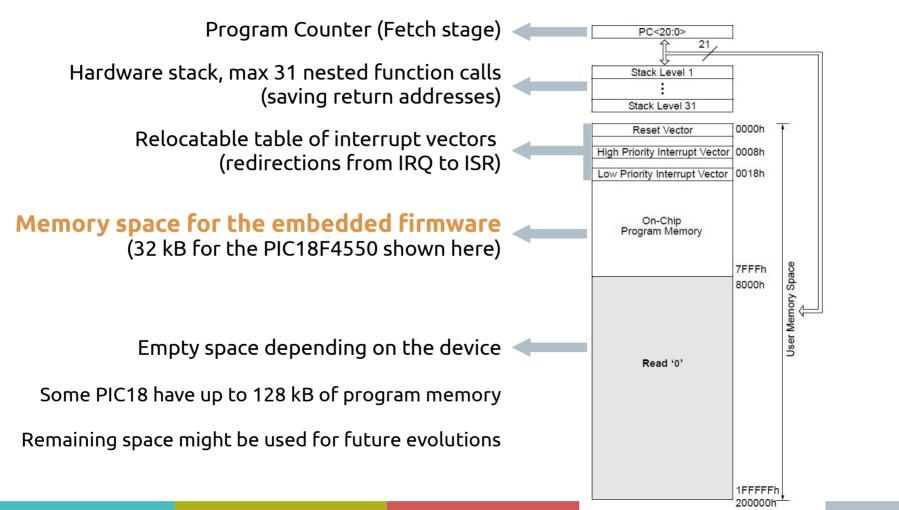

#### PIC18F4550 program memory map

22

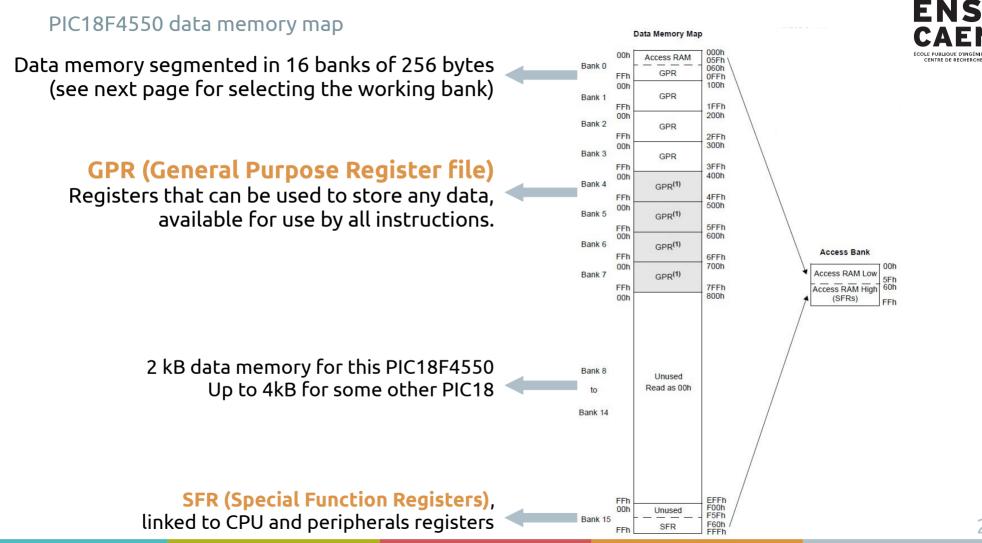

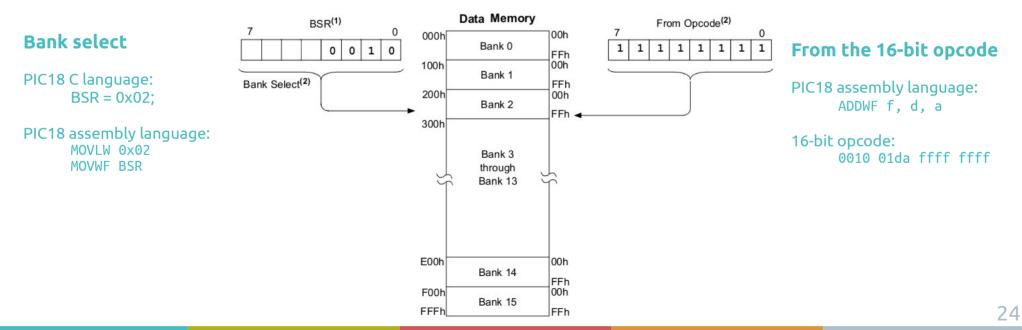

#### Data memory: Bank selection

The data memory is segmented in 16 banks of 256 bytes. This is a typical construction on 8-bit architectures.

The working bank is selected by configuring four bits in the BSR (Bank Select Register).

Then instructions that use a file-register operand will access to the data with 8-bit direct addressing mode.

Data memory: Special Function Registers (SFR)

# The SFR bank is a part of the RAM data memory where CPU and peripheral registers are mapped.

It means registers are physically outside of the memory but they are accessible with a memory address.

#### Core memory mapped registers Peripheral specialised functions memory mapped registers

| Address | Name                    | Address | Name                    | Address | Name                  | A | ddress | Name                 | Address | Name                   |

|---------|-------------------------|---------|-------------------------|---------|-----------------------|---|--------|----------------------|---------|------------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>    | FBFh    | CCPR1H                | ] | F9Fh   | IPR1                 | F7Fh    | UEP15                  |

| FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(1)</sup> | FBEh    | CCPR1L                |   | F9Eh   | PIR1                 | F7Eh    | UEP14                  |

| FFDh    | TOSL                    | FDDh    | POSTDEC2 <sup>(1)</sup> | FBDh    | CCP1CON               |   | F9Dh   | PIE1                 | F7Dh    | UEP13                  |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup>  | FBCh    | CCPR2H                |   | F9Ch   | (2)                  | F7Ch    | UEP12                  |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(1)</sup>   | FBBh    | CCPR2L                |   | F9Bh   | OSCTUNE              | F7Bh    | UEP11                  |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | CCP2CON               |   | F9Ah   | (2)                  | F7Ah    | UEP10                  |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | (2)                   |   | F99h   | (2)                  | F79h    | UEP9                   |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | BAUDCON               |   | F98h   | (2)                  | F78h    | UEP8                   |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | ECCP1DEL              |   | F97h   | (2)                  | F77h    | UEP7                   |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | ECCP1AS               |   | F96h   | TRISE <sup>(3)</sup> | F76h    | UEP6                   |

| FF5h    | TABLAT                  | FD5h    | TOCON                   | FB5h    | CVRCON                |   | F95h   | TRISD <sup>(3)</sup> | F75h    | UEP5                   |

| FF4h    | PRODH                   | FD4h    | (2)                     | FB4h    | CMCON                 |   | F94h   | TRISC                | F74h    | UEP4                   |

| FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | TMR3H                 |   | F93h   | TRISB                | F73h    | UEP3                   |

| FF2h    | INTCON                  | FD2h    | HLVDCON                 | FB2h    | TMR3L                 |   | F92h   | TRISA                | F72h    | UEP2                   |

| FF1h    | INTCON2                 | FD1h    | WDTCON                  | FB1h    | T3CON                 |   | F91h   | (2)                  | F71h    | UEP1                   |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | SPBRGH                |   | F90h   | (2)                  | F70h    | UEP0                   |

| FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H                   | FAFh    | SPBRG                 |   | F8Fh   | (2)                  | F6Fh    | UCFG                   |

| FEEh    |                         | FCEh    | TMR1L                   | FAEh    | RCREG                 |   | F8Eh   | (2)                  | F6Eh    | UADDR                  |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON                   | FADh    | TXREG                 |   | F8Dh   | LATE <sup>(3)</sup>  | F6Dh    | UCON                   |

| FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | TMR2                    | FACh    | TXSTA                 |   | F8Ch   | LATD <sup>(3)</sup>  | F6Ch    | USTAT                  |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | PR2                     | FABh    |                       |   | F8Bh   | LATC                 | F6Bh    | UEIE                   |

| FEAh    | FSR0H                   | FCAh    | T2CON                   | FAAh    | (2)                   |   | F8Ah   | LATB                 | F6Ah    | UEIR                   |

| FE9h    | FSR0L                   | FC9h    | SSPBUF                  | FA9h    | EEADR                 |   | F89h   | LATA                 | F69h    | UIE                    |

| FE8h    | WREG                    | FC8h    | SSPADD                  | FA8h    | EEDATA                |   | F88h   | (2)                  | F68h    | UIR                    |

| FE7h    | INDF1 <sup>(1)</sup>    | FC7h    | SSPSTAT                 | FA7h    | EECON2 <sup>(1)</sup> |   | F87h   | (2)                  | F67h    | UFRMH                  |

| FE6h    |                         | FC6h    | SSPCON1                 | FA6h    | EECON1                |   | F86h   | (2)                  | F66h    | UFRML                  |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FC5h    | SSPCON2                 | FA5h    |                       |   | F85h   | (2)                  | F65h    | SPPCON <sup>(3)</sup>  |

| FE4h    | PREINC1 <sup>(1)</sup>  | FC4h    | ADRESH                  | FA4h    | (2)                   |   | F84h   | PORTE                | F64h    | SPPEPS <sup>(3)</sup>  |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FC3h    | ADRESL                  | FA3h    | (2)                   |   | F83h   | PORTD <sup>(3)</sup> | F63h    | SPPCFG <sup>(3)</sup>  |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2                  |   | F82h   | PORTC                | F62h    | SPPDATA <sup>(3)</sup> |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2                  |   | F81h   | PORTB                | F61h    | _(2)                   |

| FE0h    | BSR                     | FC0h    | ADCON2                  | FA0h    | PIE2                  |   | F80h   | PORTA                | F60h    | (2)                    |

#### Data memory: Access bank

5Fh 60h

(SFRs)

When executing an operation that uses direct addressing, the execution stage checks the <a> field (access bank):

<a> = '0' or '1'ADDWF f, d, a

If <a> = '0' the CPU only sees the access bank (top half of the bank #0 + SFR bank). The 4 most significant bits of the 12-bit data memory address come from the access bank register (0x0 or 0xF)  $\rightarrow$  **Fast solution**.

If  $\langle a \rangle = '1'$  the CPU can access to all the data memory. It uses the value of the BSR (Bank Select Register) to generate the 4 most significant bits of the 12-bit data memory address.

Data memory

Find following items in this schematic

Data memory

BSR (Bank Select Register)

Access bank register

Note how they are placed relatively to each other and how the 12-bit data memory address is built.

#### PIC18 architecture

Definition

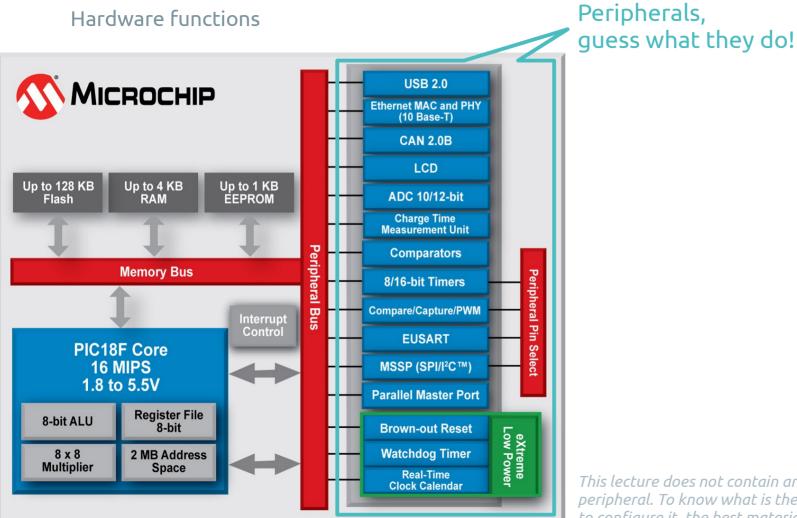

A peripheral is a hardware function that can be used to perform specific calculus and/or process some operation while letting the CPU performing something else.

For all MCUs, peripherals are physically connected to the data bus and their internal registers are mapped to the data memory.

From the program point of view, accessing to a register (read or write) is the same as accessing to a data memory cell.

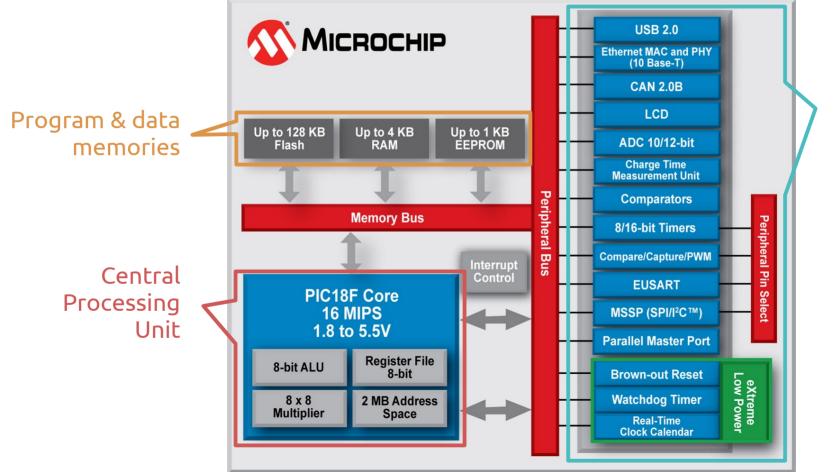

Example of PIC18F27/47K40 CPU and peripherals.

This lecture does not contain any material for using each peripheral. To know what is the role of a peripheral and how to configure it, the best material is the device datasheet. **31**

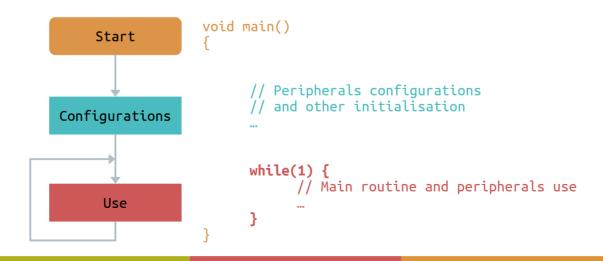

Configuration, activation, use

When the processor starts (after power-on or reset), no peripheral function is configured nor activated.

The programmer must explicitly configure and activate hardware services that are needed for the application. Only then the peripherals can be used.

Most of peripherals have configuration registers that must be set once in addition to working registers that contains updated values.

#### PERIPHERALS I/O ports

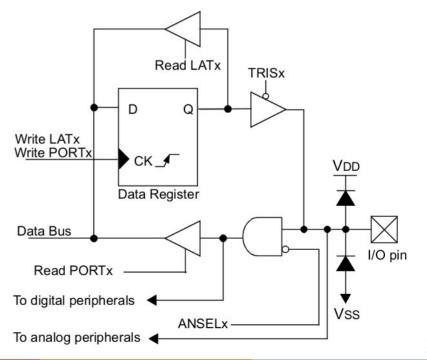

#### A port is a group of 8 pins or GPIOs (General Purpose Input/Output).

They can be used as independent digital inputs and/or outputs. The PIC18F27K40 has 5 ports (port A to port E), which makes 40 independent GPIOs available.

Each port has eight registers to control the operation. These registers are:

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- TRISx registers (data direction)

- ANSELx registers (analog select)

- WPUx registers (weak pull-up)

- INLVLx (input level control)

- SLRCONx registers (slew rate control)

- ODCONx registers (open-drain control)

#### Example of GPIO (General Purpose Input/Output) on the Curiosity HPC board.

First the RA4 pin is configured as an output, then the output value is set to 'high'. This will turn on the LED D2 on this pin.

| PIC18 C program                                 | PIC18 assembly program                             |  |

|-------------------------------------------------|----------------------------------------------------|--|

| <pre>//Set RA4 as an output TRISA = 0xEF;</pre> | ;Set RA4 as an output<br>MOVLW 0xEF<br>MOVWF TRISA |  |

| <pre>//Set RA4 to high level LATD = 0x10;</pre> | ;Set RA4 to high level<br>MOVLW 0x10<br>MOVWF LATA |  |

RA4 = pin 4 of port A (also bit 4 of registers associated to port A).

TRISx = register that contains the direction of the 8 pins of the port x ('0' = Output, '1' = Input).

LATx = register that contains the output value for pins configured as outputs in port x.

#### Input/output interfaces

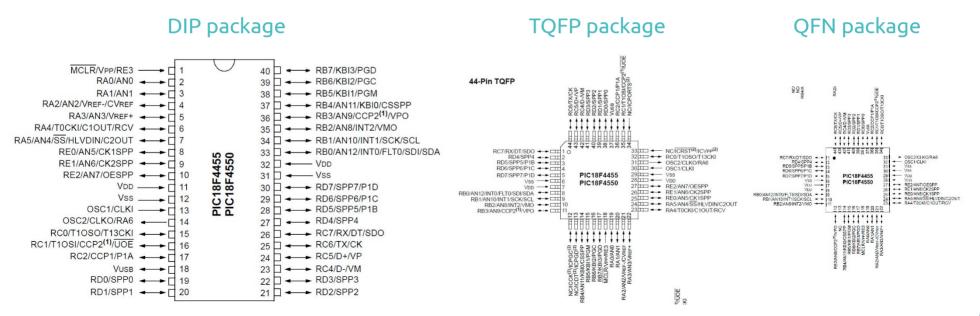

MCUs usually have more peripherals than they can really handle.

In fact, many peripherals are connected to the same pins. This implies that some peripherals cannot be used at the very same time.

As many input and output pins can be used by several peripherals, connections between pins and peripherals must be set using the Peripheral Pin Select (PPS) module.

Reference clock module

Like all other MCUs, the PIC18 family offers configuration and system hardening services.

"Hardening" an application consists in making it less sensitive to its environment (power supply fluctuations, ...) or even handle unexpected situations (watchdog, ...).

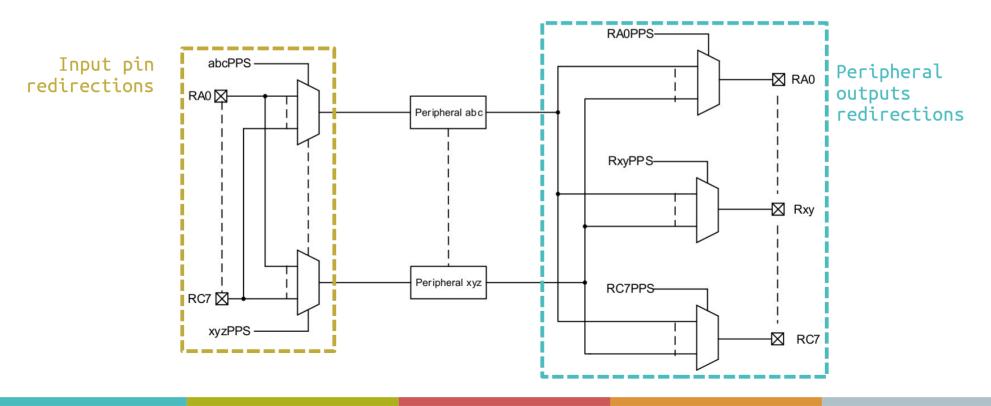

Any program on PIC18 must start with this configuration:

/\* CPU specific features configuration \*/

#pragma config PLLDIV=2, CPUDIV=0SC1\_PLL2, F0SC=HSPLL\_HS

#pragma config BOR=0FF, WDT=0FF, MCLRE=ON, LVP = 0FF

#### PERIPHERALS

#### Reference clock module

# #pragma config PLLDIV=2, CPUDIV=0SC1\_PLL2, F0SC=HSPLL\_HS

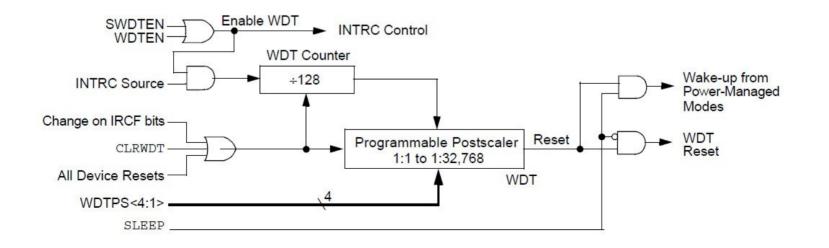

The watchdog is an application agent.

In normal circumstances, the application resets the watchdog timer at regular intervals.

When the application remains stuck for a long time, the watchdog timer is not reset and will eventually overflow. The watchdog will force the application to reboot by resetting the CPU.

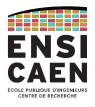

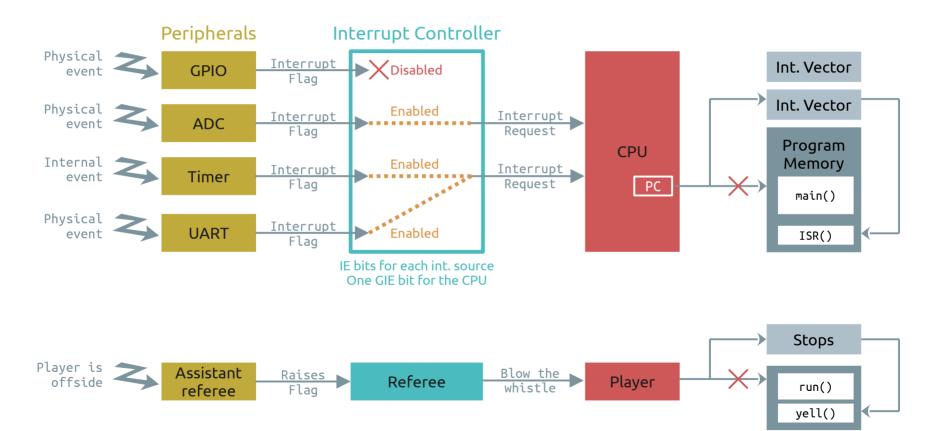

Event Interrupt Flag (IF) Interrupt Request (IRQ) Interrupt Service Routine (ISR)

Interrupt flag

### Once a peripheral has been configured, it becomes autonomous.

When its job is done (counting, converting, ...) or when a special event occurs (message received, switch pressed, ...), the peripheral will raise a Interrupt Flag (IF).

A interrupt flag is a bit in a register, each flag corresponding to a precise event.

Peripheral Interrupt Request (Flag) Register 0

| Bit    | 7 | 6 | 5      | 4     | 3 | 2      | 1      | 0      |

|--------|---|---|--------|-------|---|--------|--------|--------|

|        |   |   | TMR0IF | IOCIF |   | INT2IF | INT1IF | INTOIF |

| Access |   |   | R/W    | R     |   | R/W    | R/W    | R/W    |

| Reset  |   |   | 0      | 0     |   | 0      | 0      | 0      |

Bit 5 – TMR0IF Timer0 Interrupt Flag bit<sup>(1)</sup>

| Value | Description                                                |

|-------|------------------------------------------------------------|

| 1     | TMR0 register has overflowed (must be cleared by software) |

| 0     | TMR0 register has not overflowed                           |

#### Bit 4 – IOCIF Interrupt-on-Change Flag bit<sup>(1,2)</sup>

| Value | Description                                          |

|-------|------------------------------------------------------|

| 1     | IOC event has occurred (must be cleared by software) |

| 0     | IOC event has not occurred                           |

#### Bits 0, 1, 2 – INTxIF External Interrupt 'x' Flag bit<sup>(1,3)</sup>

| Value | Description                             |

|-------|-----------------------------------------|

| 1     | External Interrupt 'x' has occurred     |

| 0     | External Interrupt 'x' has not occurred |

Interrupt Service Routine (ISR)

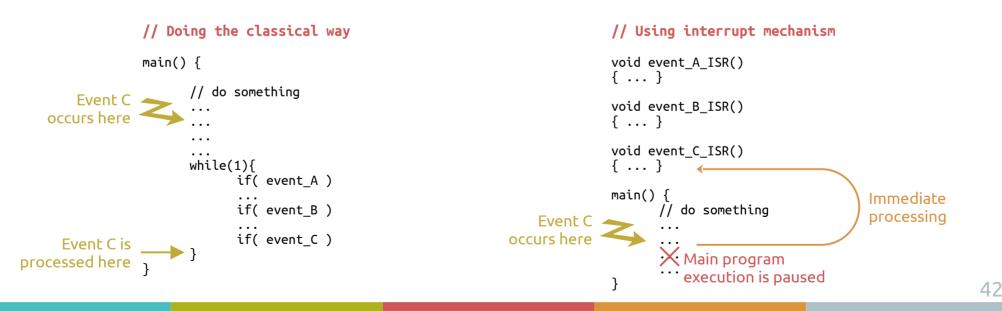

However some events require immediate attention. Plus, using interrupt flags the same way as classical variables (e.g. testing them in "if" statements) is inefficient.

That is why an **interrupt mechanism** has been designed. This is the hardware way of stopping the normal execution flow of the CPU. It will then switch to the execution of a function dedicated to the event: the **ISR (Interrupt Service Routine)**.

Interrupt Request (IRQ)

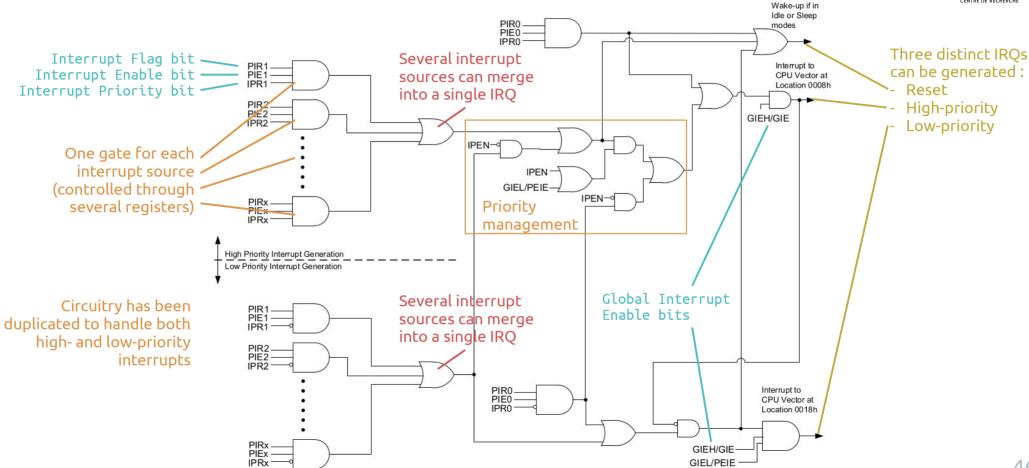

All interrupts are disabled by default: it is the programmer work to decide and explicitly tell which event is worthy enough to lead to an interrupt.

To do so, the programmer must configure the **Interrupt controller**.

This circuit will turn selected interrupt flags into **Interrupt Requests (IRQ)**, that will cause the CPU to stop its current work.

Interrupt flag

Bit in a register that *indicates* that an event has occurred.

#### Interrupt request

Physical wire connected to the CPU that *makes it switch to another function*.

#### Notes

Many interrupt flags can be linked onto the same IRQ signal. A specific IRQ corresponds to a specific ISR. Interrupt controller

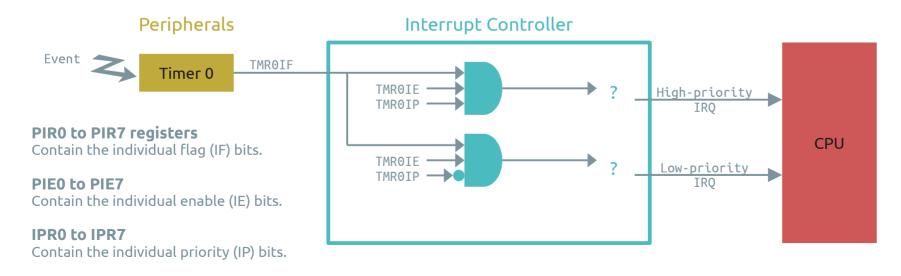

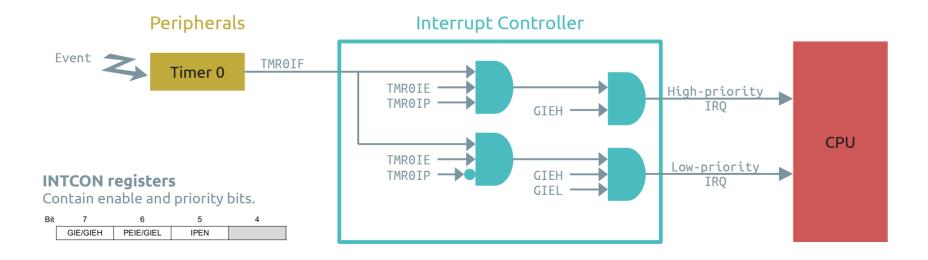

The **interrupt controller** consists of AND and OR gates. This circuitry independently let or prevent interrupt flags becoming interrupt requests.

To do so, one must configure the registers of the interrupt controller. Like the PIC18, most MCUs need to configure three bits for each interrupt:

the Interrupt Flag (IF) bit, the Interrupt Enable (IE) bit, the Interrupt Priority (IP) bit.

Interrupt controller

After configuring the interrupt controller for every single interrupt source, one last parameter should allow the CPU to see IRQ signals.

Most MCUs have a Global Interrupt Enable (GIE) bit to do so. The PIC18 has two of them: GIEH and GIEL for respectively high- and low-priority interrupts.

#### Interrupt controller: PIC18F27/47K40 interrupt controller logic

Interrupt Service Routine (ISR)

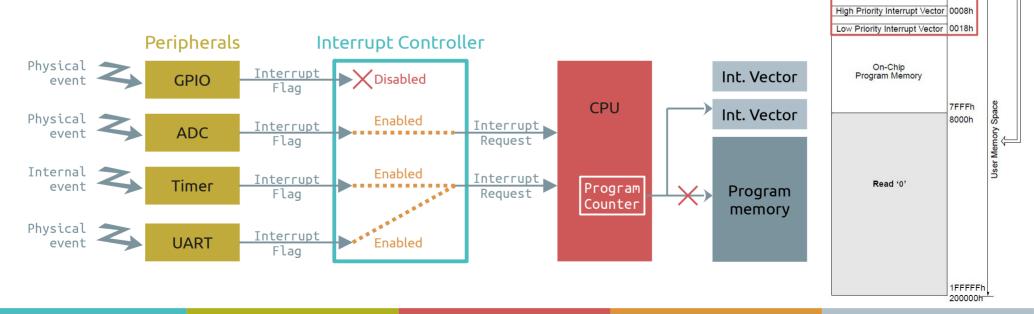

**Interrupt Service Routines (ISR)** are functions called by the **Interrupt vectors**, which are specific parts of the Flash memory.

When the CPU sees an **Interrupt Request (IRQ)**, it pauses its main program and branches automatically to the corresponding interrupt vector, causing the execution of the Interrupt Service Routine.

Interrupt Service Routine (ISR)

ISRs are not proper functions: they should not be called from the main program.

They are automatically called whenever the CPU sees the IRQ signals (this is called "event-driven programming", fr: *programmation évènementielle*)

As ISRs are called at unpredictable moments, it is not possible to pass arguments to the ISR functions.

In order to exchange information between the main program and the ISRs, global variables can be used.

But remember global variables are shared resources and be used very carefully!

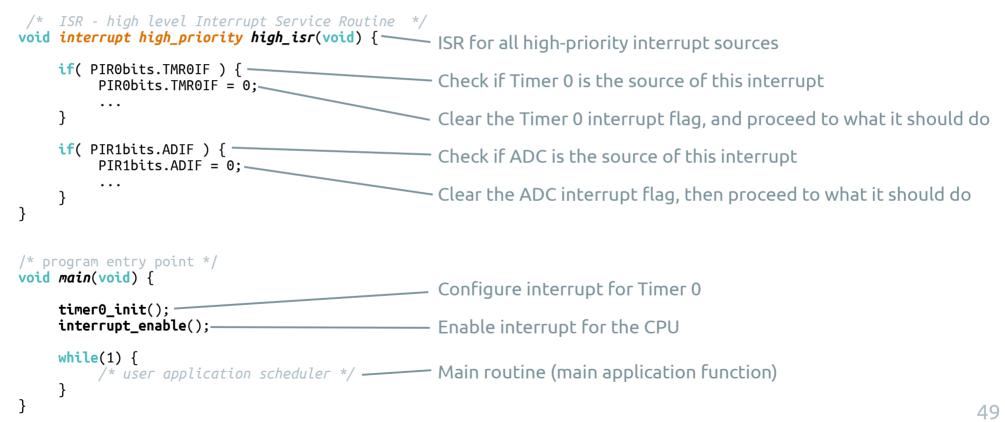

#### Interrupt Service Routine (ISR)

## Here is an example of how writing an ISR using the Microchip XC8 toolchain.

Interrupt vector

## Interrupt vectors are very small areas in the Flash memory.

- $\rightarrow$  16 bytes for the high-priority interrupt vector

- ightarrow 2 bytes for the low-priority interrupt vector

In fact, those areas are too small to contain the ISR but they are large enough to contain CALL or GOTO instructions, which will actually call the ISR (see next page).

Technically ISR are stored in the program memory, but they should be accessed only through interrupt vectors.

Context switch

As an ISR can be called at anytime, it will break the **context** that the main program is using (values of W-reg, STATUS, BSR for the PIC18). All registers must be saved in order to return to prior values when the ISR has ended.

The PIC18 toolchain will usually implement a hardware context backup for the highpriority ISR and a software context backup for the low-priority ISR.

| Hardware context backup |  |

|-------------------------|--|

| (CPU shadow registers)  |  |

high\_vector: CALL high\_isr, 1

#### high\_isr:

```

; user program - ISR processing

RETFIE 1

```

Hardware context backup (Flash memory)

| low_vector:<br>GOTO | low_isr      |              |

|---------------------|--------------|--------------|

| low_isr:            |              |              |

| MOVWF               | wreg_tmp     |              |

| MOVFF               | STATUS,      | status_tmp   |

| MOVFF               | BSR,         | bsr_tmp      |

| ; user              | program - IS | R processing |

| MOVFF               | bsr_tmp,     | BSR          |

| MOVFF               | status tmp,  | STATUS       |

| MOVF<br>RETFIE      | wreg_tmp,    | W            |

#### Summary

#### PIC18 architecture

#### CONTACT

## Dimitri Boudier – PRAG ENSICAEN

dimitri.boudier@ensicaen.fr

## With the precious help of:

- Hugo Descoubes (PRAG ENSICAEN)

- Bogdan Cretu (MCF ENSICAEN)