# **LANGAGE VHDL**

L'École des INGÉNIEURS Scientifiques

1

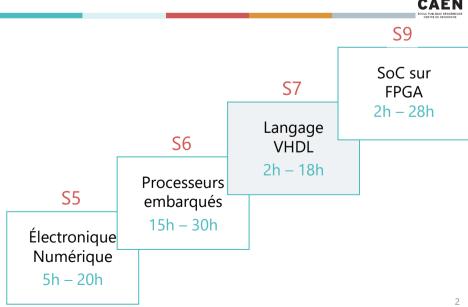

# 1. CONTEXTE: MAQUETTE PÉDAGOGIQUE

# 1. CONTEXTE : ÉLECTRONIQUE NUMÉRIQUE

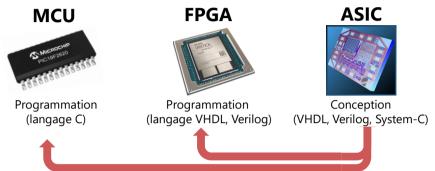

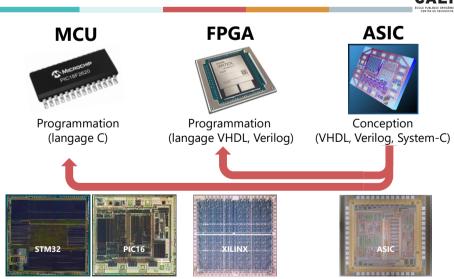

Quelles solutions matérielles pour réaliser une fonction d'électronique numérique ?

VHDL (Verilog) : pour la programmation de FPGA applications nécessitant de la vitesse de traitement, pour la conception de circuit.

3

# 1. CONTEXTE : ÉLECTRONIQUE NUMÉRIQUE

VHDL (Verilog): pour la conception.

4

# 1. CONTEXTE : ÉLECTRONIQUE NUMÉRIQUE

Les designers d'INTEL (les concepteurs des autres CPU et MCU) utilisent VHDL et Verilog pour la conception des microprocesseurs et microcontrôleurs.

#### Average Hardware Design Engineer with Verilog VHDL Skills Salary

#### Average Hardware Design Engineer with C Programming Language Skills Salary

5

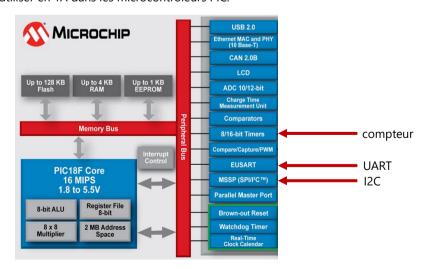

#### 2. LE MCU « PIC18F27K40 »

7

Lors des TP, vous développerez des périphériques comme ceux que vous avez pu utiliser en 1A dans les microcontrôleurs PIC.

# Le composant FPGA

Matthieu DENOUAL

L'École des INGÉNIEURS Scientifiques

1

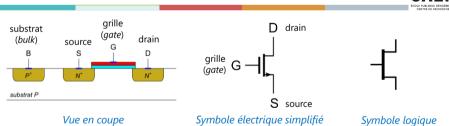

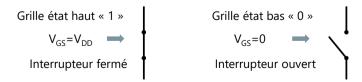

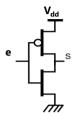

#### 1.1. LE TRANSISTOR NMOS

- > En logique, le transistor est utilisé en interrupteur commandé.

- L'interrupteur se situe entre le drain et la source.

- La commande le l'interrupteur se fait par la tension V<sub>GS</sub> (entre Grille et Substrat).

2

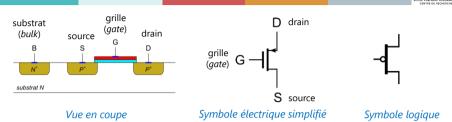

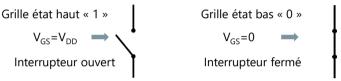

#### 1.2. LE TRANSISTOR PMOS

- Comme son dual, le transistor PMOS est aussi utilisé en interrupteur commandé.

- Il y a une complémentarité entre les deux types, que ce soit au niveau de la structure ou au niveau du fonctionnement.

- La technologie CMOS (Complementary MOS) exploite cette complémentarité.

3

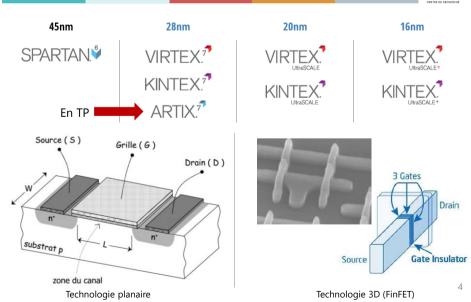

# 1.3. TECHNOLOGIE MICROÉLECTRONIQUE

#### 1.4. L'INVERSEUR

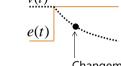

Illustration du temps de propagation quand e passe de 0 à 1

Structure

Double inversion

Schémas équivalents

Symbole

Changement d'état de s(t) à  $v(t)=V_{dd}/2$

Il y a un temps de propagation dans tout circuit logique. Sa connaissance permet d'adapter la fréquence de travail.

5

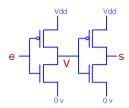

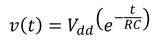

#### 1.5. LA PORTE NAND

Symboles

- La porte NAND à 2 entrées, en technologie CMOS est constituée de 4 transistors.

- Toute fonction logique combinatoire peut être réalisée à partir de portes NAND.

Ce qui en fait une porte universelle.

- La porte NAND est choisie comme unité de mesure pour évaluer la densité d'un circuit logique programmable.

- Exemple : un composant de densité 1000 portes peut embarquer une logique équivalente à 1000 portes NAND.

6

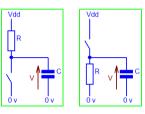

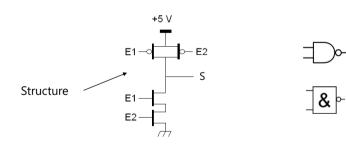

#### 1.6. LA PORTE ANALOGIQUE

- Commande = 0L: les deux transistors présentent une impédance quasi infinie entre le drain et la source, le circuit se comporte comme un interrupteur ouvert

- Commande = 1L: les deux transistors en parallèle présentent une faible résistance R<sub>ON</sub> équivalente entre le drain et la source, le circuit se comporte comme un interrupteur fermé

7

7

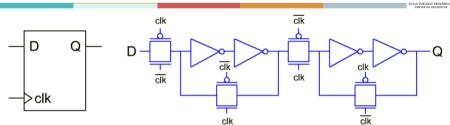

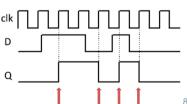

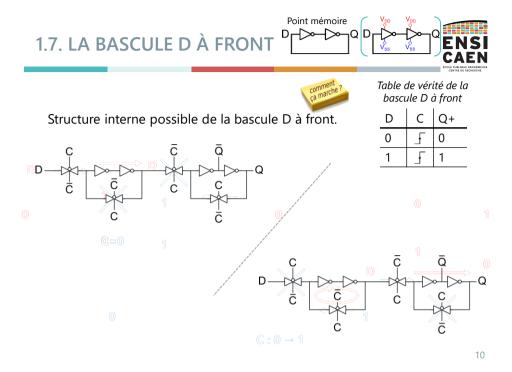

# 1.7. LA BASCULE D À FRONT

- La bascule D recopie l'entrée D sur la sortie Q sur front montant de clk.

- C'est un composant qui fige une situation comme le ferait un appareil photo.

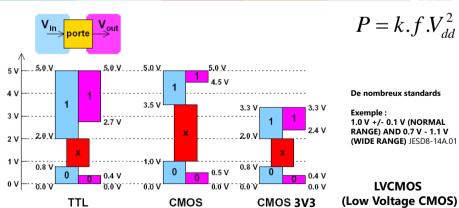

# 2.1. TENSIONS ET NIVEAUX LOGIQUES

- Les fourchettes des niveaux logiques fixent les règles de dialogue entre les circuits tout en garantissant une immunité au bruit.

- Pour réduire la puissance consommée, on diminue la tension d'alimentation. Jusqu'à quelle valeur?

Joint Electron Device Engineering Council

JEDEC Solid State Technology Association Document

11

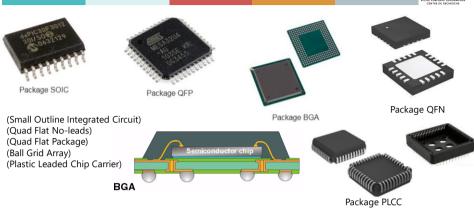

#### 2.2. LES BOITIERS BGA

- Les boitiers de type BGA ont révolutionné la microélectronique en faisant exploser le nombre de broches > 1000.

- Le montage en surface de ces boitiers permet des économies non négligeables.

- La taille des composants se trouve réduite par la même occasion.

13

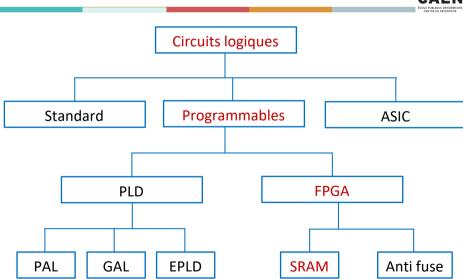

## 2.3. CLASSIFICATION DES CIRCUITS LOGIQUES

14

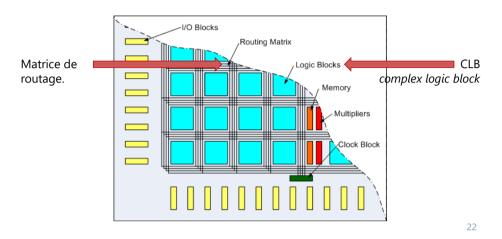

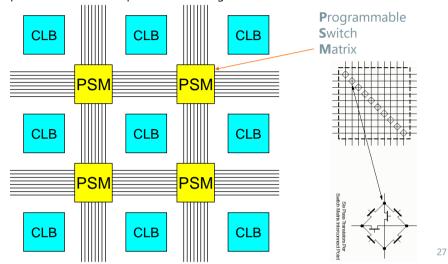

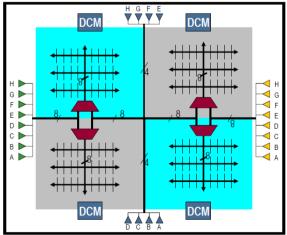

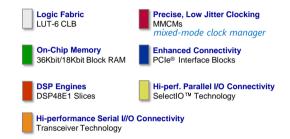

#### 3.1. ARCHITECTURE DES FPGA

Un circuit FPGA est une matrice symétrique comportant des ressources pour la logique, les entrées-sorties, les interconnexions et bien plus encore.

22

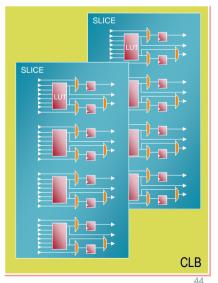

#### 3.2. LE BLOC LOGIQUE CONFIGURABLE (CLB) COUT ΥB G4 G3 G2 G1 Carry Carry D СК cĸ Control Control Logic EC Logic F5IN-F5IN BY -F4 F3 F2 F1 Carry F4 F3 F2 F1 D CK Control Control EC Logic Logic

- Chaque CLB comporte 2 tranches (SLICE).

- Un slice contient 2 paires de (LUT + bascule + retenue).

- 2 buffers 3 états (BUFT) sont associés à chaque CLB.

Complex Logic Block 23

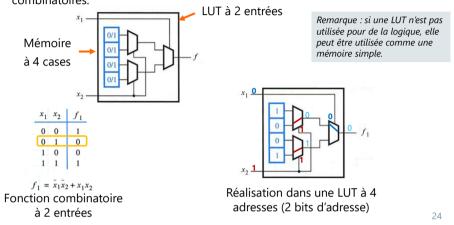

## 3.3. LOGIQUE COMBINATOIRE DANS LE FPGA

- Pour la réalisation des fonctions logiques combinatoires, les composants FPGA utilisent la technique de la table de consultation (LUT).

- Cette technique utilise des petites mémoires pour réaliser des fonctions combinatoires.

24

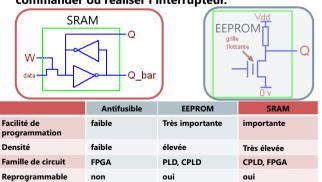

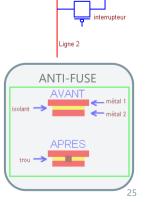

#### 3.4. TECHNOLOGIE DE PROGRAMMATION

Les composants logiques programmables comportent un ensemble de portes logiques préexistantes que l'on utilise ou non en les connectant ou non. La manière dont on les connecte entre elles crée les fonctions logiques souhaitées.

La programmation d'un composant revient à fermer ou ouvrir l'interrupteur qui relie les 2 lignes qui se croisent.

Différentes technologies sont mises en œuvre pour commander ou réaliser l'interrupteur.

Ligne 1

#### 3.5. LES MATRICES D'AIGUILLAGE

Les ressources de routage sont abondantes dans un FPGA car le routage est un point clef dans la compilation d'un design.

27

#### 3.6. ROUTAGE DE L'HORLOGE

Un réseau de routage est spécialement dédié à l'horloge pour lui permettre d'atteindre sans délai toutes les bascules du composant.

DCM : Digital Clock Manager

28

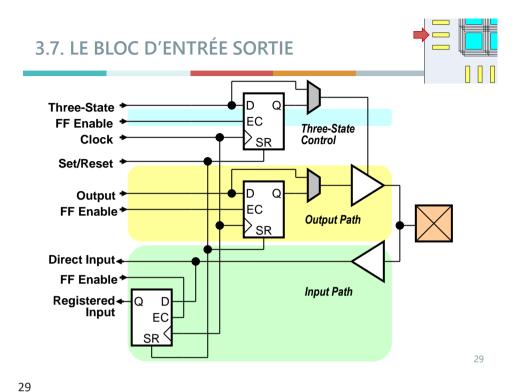

# Architecture silicium des circuits CAEN Intel Processor Core-i7 XILINX Virtex II XILINX Virtex 4 XILINX Virtex 4

3.8. ARCHITECTURE SILICIUM DU FPGA

On voit la structure régulière sous forme de matrice des FPGA par rapport aux structures processeurs

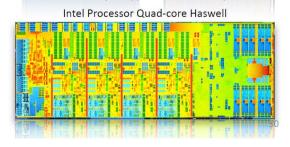

# 4.1. ACTEURS DU MARCHÉ DES FPGA

31

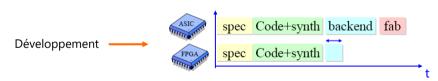

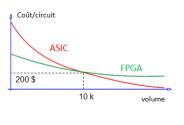

# 4.2. CHOIX ENTRE FPGA/CPLD ET ASIC

Backend = conception physique ou implémentation physique

| CRITERE                | AVANTAGE |  |  |

|------------------------|----------|--|--|

| Temps de développement | FPGA     |  |  |

| Coût petit volume      | FPGA     |  |  |

| Coût gros volume       | ASIC     |  |  |

| Performances           | ASIC     |  |  |

| Consommation           | ASIC     |  |  |

| Evolution, maintenance | FPGA     |  |  |

32

#### 4.3. SECTEURS D'APPLICATION DES FPGA

#### Automotive Device Families

- XA Spartan-6 FPGAs

- XA Spartan-3A FPGAs

- XA Spartan-3A DSP FPGAs

- XA Spartan-3E FPGAs

#### Defense-grade Device Families

- Defense-grade Artix-7Q FPGAs

- Defense-grade Kintex-7Q FPGAs

- Defense-grade Virtex-7Q FPGAs

- Defense-grade Virtex-6Q FPGAs

- Defense-grade Spartan-6Q FPGAs

- Defense-grade Virtex-5Q FPGAs

- Defense-grade Virtex-4Q FPGAs

#### Space-grade Device Families

- Space-grade Virtex-5QV FPGAs

- Space-grade Virtex-4QV FPGAs

33

33

# 8.1. LES COMPOSANTS DE LA SÉRIE 7

TP\_\_

|                            | ARTIX.7               | KINTEX.7                             | VIRTEX.7                                 |

|----------------------------|-----------------------|--------------------------------------|------------------------------------------|

| Maximum Capability         | Lowest Power and Cost | Industry's Best<br>Price/Performance | Industry's Highest<br>System Performance |

| Logic Cells                | 20K – 355K            | 70K – 480K                           | 285K – 2,000K                            |

| Block RAM                  | 12 Mb                 | 34 Mb                                | 65 Mb                                    |

| DSP Slices                 | 40 – 700              | 240 – 1,920                          | 700 – 3,960                              |

| Peak DSP Perf.             | 504 GMACS             | 2,450 GMACs                          | 5,053 GMACS                              |

| Transceivers               | 4                     | 32                                   | 88                                       |

| Transceiver<br>Performance | 3.75Gbps              | 6.6Gbps and 12.5Gbps                 | 12.5Gbps,<br>13.1Gbps and 28Gbps         |

| Memory Performance         | 1066Mbps              | 1866Mbps                             | 1866Mbps                                 |

| I/O Pins                   | 450                   | 500                                  | 1,200                                    |

| I/O Voltages               | 3.3V and below        | 3.3V and below<br>1.8V and below     | 3.3V and below<br>1.8V and below         |

42

#### 8.2. UNE ARCHITECTURE ALIGNÉE

# Common elements enable easy IP reuse for quick design portability across all 7 series families

- Design scalability from low-cost to high-performance

- Expanded eco-system support

- Quickest TTM (Time To Market)

Artix™-7 FPGA

Kintex™-7 FPGA

IP: Intellectual Property

43

# 8.3. LE BLOC LOGIQUE

43

#### Two side-by-side slices per CLB

- Slice\_M are memory-capable

- Slice\_L are logic and carry only

#### Four 6-input LUTs per slice

- Consistent with previous architectures

- Single LUT in Slice\_M can be a 32-bit shift register or 64 x 1 RAM

#### Two flip-flops per LUT

Excellent for heavily pipelined designs

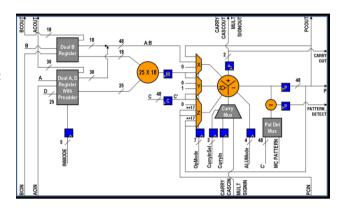

#### 8.4. LE BLOC DSP

#### All 7 series FPGAs share the same DSP slice

- 25x18 multiplier

- 25-bit pre-adder

- Flexible pipeline

- Cascade in and out

- Carry in and out

- 96-bit MACC

- 48-bit ALU

- 17-bit shifter

- Dynamic operation (cycle by cycle)

45

45

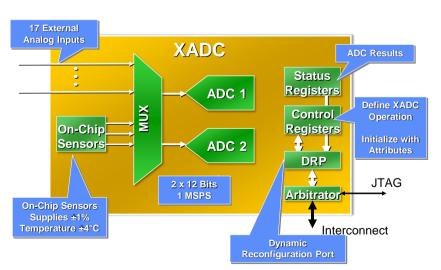

#### 8.5. LE CONVERTISSEUR ADC

46

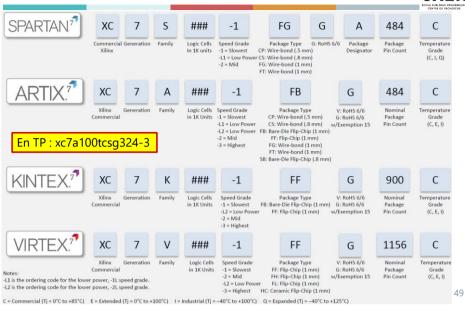

# 8.6. RÉFÉRENCES DE LA FAMILLE 7

49

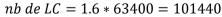

#### 8.7. NOTION DE « LOGIC CELL »

|             |                                                         |         |         |         | ÉCOLE PUBLIQUE D'INSÉNIEURS<br>CENTRE DE RECHERCHE |  |

|-------------|---------------------------------------------------------|---------|---------|---------|----------------------------------------------------|--|

|             | Artix®-7 FPGAs                                          |         |         |         |                                                    |  |

|             | Optimized for Lowest Cost and Lowest Power Applications |         |         |         |                                                    |  |

|             | (1.0V, 0.95V, 0.9V)                                     |         |         |         |                                                    |  |

| Part Number | XC7A15T                                                 | XC7A35T | XC7A50T | XC7A75T | XC7A100T                                           |  |

| Logic Cells | 16,640                                                  | 33,280  | 52,160  | 75,520  | 101,440                                            |  |

| Slices      | 2,600                                                   | 5,200   | 8,150   | 11,800  | 15,850                                             |  |

- Une « logic cell » représente une LUT à 6 entrées. La logique de calcul de retenue est comptabilisée en appliquant un coefficient 1,6.

- 1 LC = 1.6 LUT

- Chaque LUT est associée à 2 bascules D.

- Prenons en exemple le composant XC7A100T

Pour Artix-7, chaque logic slice contient 4 LUT 6 entrées

$$nb \ de \ LUT = 4 * 15850 = 63400$$

50

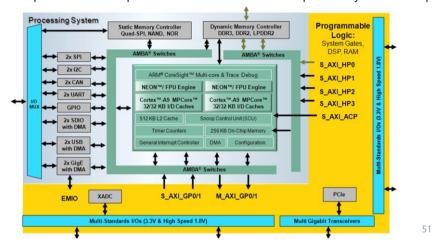

#### 9. LE COMPOSANT ZYNQ 7000

- Il embarque un processeur ARM9 à 2 cœurs, des contrôleurs de différents types de mémoires, diverses interfaces et de la logique programmable.

- Ces 2 parties communiquent via un bus AXI. Circuit idéal pour les System On Chip.

51

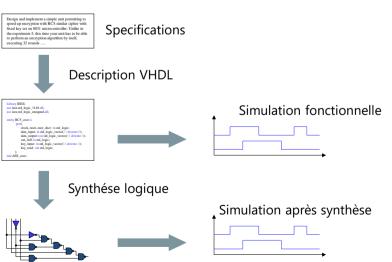

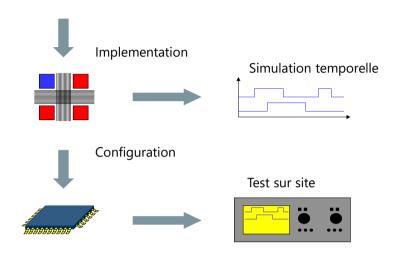

# 10.1. DÉVELOPPEMENT

52

#### **DÉVELOPPEMENT-SUITE**

53

53

# 10.1. DÉVELOPPEMENT

55

# TO.1. DÉVELOPPEMENT ENSIGNATION PROCESSANDA CONTROLLA DE LA CONTROLLA DE LA

Fonctions élémentaires : registres, multiplexeurs, additionneurs, ...

## PARTICION OF CONTRIBUTION O

56

(Register Transfer Level)

# 10.1. DÉVELOPPEMENT - IMPLÉMENTATION PROPERTIES DE L'ANDIE DE L'A

57

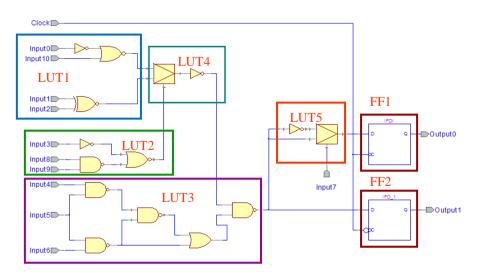

# 10.2. IMPLÉMENTATION - MAPPING

58

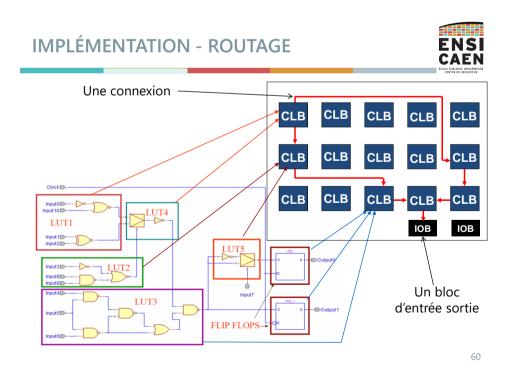

#### IMPLÉMENTATION - PLACEMENT **ENSI** CLB CLB CLB CLB **CLB** CLB LUT4 → IOB IOB LUT3 FLIP FLOPS 59

59

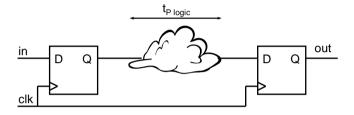

#### 10.3. LE CHEMIN CRITIQUE

- Chemin critique = chemin reliant deux bascules et ayant le plus long délai.

- C'est de lui que dépendra la fréquence maximale de l'horloge.

- Période minimale d'horloge = délai du chemin critique.

- Celle-ci est calculée automatiquement par les outils de développement IDE.

$$t_{Critical} = t_{P\,FF} + t_{P\,\,logic} + t_{S\,\,FF}$$

61

# Le langage VHDL

Matthieu DENOUAL

L'École des INGÉNIEURS Scientifiques

1

### 1.1. PRÉSENTATION

- Vhsic Hardware Description Langage (Vhsic = Very High Speed Integrated Circuit) est un langage de description de matériel et non un langage software comme le C.

- Standardisé en 1987 par l'IEEE (Institute Of Electrical and Electronics Engineers) sous la référence IEEE 1076-87. Une mise à jour importante a été faite en 1993 : IEEE 1076-93 est supportée par tous les outils. Dernière révision en 2008.

- Utilisé au début pour la modélisation et la simulation avant d'être adopté pour la synthèse logique. Toute la syntaxe n'est pas synthétisable !!!

simulation

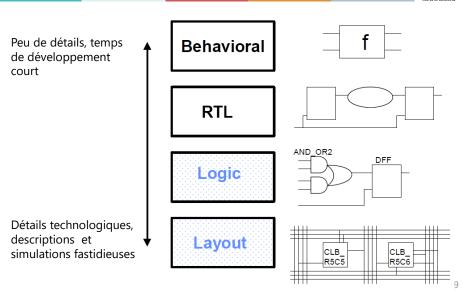

- Permet de décrire un système avec un niveau d'abstraction élevé « algorithmique » ou un niveau proche du matériel « gate level ». Entre les deux se trouve le niveau RTL « Register Transfert Level ».

- C'est le niveau RTL qui est utilisé pour la synthèse car il est moins lourd que le niveau « gate level » et il est indépendant de la cible. Le niveau « algorithmique » n'est pas forcément synthétisable.

- 70% de la syntaxe ADA : langage de programmation orienté objet de 1980 utilisé dans les systèmes temps réel et embarqués nécessitants fiabilité et sécurité.

#### 1.1. PRÉSENTATION

Différences entre langage informatique (exemple langage C) et VHDL:

#### langage informatique

Sous-programme (fonction, procédure) : Début durée

Fin

Variables : temps de vie limité

A = B;

A = C;

Derrière le code :

Mémoire programme, mémoire données, architecture matérielle figée

#### **VHDL**

Composant:

Décrit une partie du matériel

Hors du temps

Permanent

Concurrent → langage parallèle

Signaux : représentent une connexion entre composants

A <= B;

$A \le C$ ; B et C connectés à A

Derrière le code :

Structure matérielle, connectique

Langage informatique pour électronicien

3

3

# 1.2. LA SYNTHÈSE LOGIQUE

4

4

end Behavioral\_3p;

#### 1.3. SIMULATION / SYNTHÈSE

- On rencontre deux langages de description de matériel : VHDL (populaire en Europe, proche de Ada « pgm objet ») et Verilog (populaire aux US).

- Le langage VHDL permet de :

- 1. Modéliser des circuits pour la simulation

- 2. Décrire des applications pour circuits ASIC ou programmables (FPGA)

Modélisation pour la simulation

Description de système matériel

#### Norme IEEE 1076

La totalité de la norme peut être utilisée pour la modélisation

#### Norme IEEE 1076

Une partie seulement peut être utilisée pour la synthèse

X <= '1' after 100 ns;

Wait for 200 ns;

Signal ent\_s : std\_logic := '0'</pre>

Les instructions after et wait à gauche ne peuvent pas être utilisées pour la synthèse

5

5

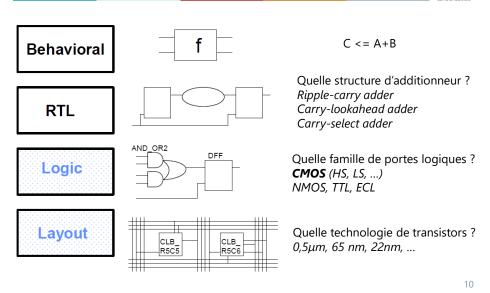

#### 1.4. NIVEAUX D'ABSTRACTION

9

#### 1.4. NIVEAUX D'ABSTRACTION

10

#### 2.1. PREMIER EXEMPLE

VHDL : langage de description matériel (HDL : Hardware Description Langage)

```

commentaire

-- Voici un exemple simple

Appel librairies

-- La déclaration des bibliothèques

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

а

. Х

portes

b

L'entité

- у

entity portes is

Port ( a : in std_logic;

b : in std_logic;

c : in std_logic;

x : out std_logic;

y : out std_logic;

z : out std_logic;

z : out std_logic;

}

end portes;

entité

L'architecture

architecture Behavioral of portes is begin

x <= a or b;

y <= b nand (not c);

z <= a xor c;

architecture

11

```

11

#### 2.2. DEUXIÈME EXEMPLE

VHDL : langage de description matériel (HDL : Hardware Description Langage)

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

clk

Clk_div

div out

commentaire

reset

entity clk_div is

generic (N : natural := 5);

Port ( reset : in std_logic;

clk : in std_logic;

div_out : out std_logic);

end clk_div;

architecture Behavioral of clk_div is

La nouveauté dans cet exemple

signal count_temp : std_logic_vector

est le bloc « process ».

begin

-- autre commentaire

process (reset, clk)

Ce bloc est très pratique pour

begin

décrire des unités cadencées par

if reset='0' then

count_temp <= (others => '0');

elsif (clk'event and clk='1') then

une horloge.

count_temp <= count_temp + 1;</pre>

end if;

On peut écrire plusieurs process,

end process;

ils s'exécutent tous en parallèle.

div out <= count temp(N);

end Behavioral;

```

12

# IMPORTANT, À RETENIR [1/2]

Le langage VHDL est un langage de description matériel, donc par essence proche du matériel.

La description de l'entité définit les ports d'entrée/sortie. <u>Un signal correspond à un fil</u>.

```

entity ex_fils is

Fil d

(C)

Port (a: in STD_LOGIC;

b : in STD_LOGIC;

s0> ×0

a

c:in STD LOGIC;

b

s0 : out STD_LOGIC;

s1 : out STD LOGIC);

end ex_fils;

s1

Ports

architecture Flow of ex_fils is

entrée

signal d : STD_LOGIC;

Ports

begin

sortie

d <= a and (not b);

s0 <= d or c;

Ports entrée/sortie

s1 <= a or (not c);

end Flow;

Fil d en sortie de fonction logique a./b

Nom des fils reprend le nom des ports.

13

```

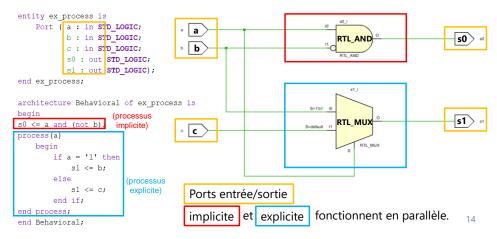

Le langage VHDL est un langage de description matériel, donc par essence proche du matériel.

Les process (processus) permettent de définir des fonctions logiques qui se déroulent en parallèle (on parlera d'exécution concurrente).

14

#### PROCESSUS IMPLICITE OU EXPLICITE

```

architecture Behavioral of circuit is

signal inter : std logic ;

begin

Equation logique

X \ll (A \text{ or } B) \text{ and } C;

(processus implicite)

process (A,C)

begin

if (A='1' and C='0') then

inter <= '1';</pre>

Début et fin

Bloc « process »

(processus explicite)

inter <= '0';

end if;

end process;

Connexion

Y <= inter;

(processus implicite)

end Behavioral;

```

Rmq

L'ordre des processus n'a pas d'importance étant donné qu'ils s'exécutent de façon concurrente.

15

#### 2.3. TROIS RÈGLES DE BASE

```

-- Programme de démonstration

Les commentaires

library IEEE; -- librairie JEEE

commencent par un

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

use IEEE.std_logic_unsigned.all;

double tiret « -- » et se

terminent à la fin de la

ligne.

entity majuscule is

Port (a: in STD_LOGIC;

b: in STD_LOGIC;

c: in STD_LOGIC;

x : out STD_LOGIC;

y : out STD_LOGIC;

z : out STD LOGIC);

VHDL ne distingue pas les

end majuscule;

majuscules des minuscules :

architecture Behavioral of majuscule is

inter et INTER désignent le

signal INTER : std_logic;

même signal

begin

inter <= a or b;

y <= not INTER;

z <= a xor c; ←

Une instruction se termine par un «; »

end Behavioral;

les espaces ne sont pas significatifs

16

```

16

#### 2.4. LA LIBRAIRIE IEEE

- Le standard « IEEE.1164 » définit une librairie avec un certain nombre de packages dont certains sont indispensables pour tout programme VHDL.

- Les packages doivent être appelés avant la déclaration de l'entité.

```

library IEEE; -- librairie IEEE

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

use IEEE.std_logic_unsigned.all;

```

L'extension « .all » du nom de la librairie signifie qu'on intègre tout le contenu.

17

#### 2.4.1. LE PACKAGE STD\_LOGIC\_1164

- C'est ici qu'est défini le type « std\_logic » qui est une extension du type « bit ».

- 'U': uninitialized. This signal hasn't been set yet.

'X': unknown. Impossible to determine this value/result.

'0': logic 0

'1': logic 1

'z': High Impedance

'W': Weak signal, can't tell if it should be 0 or 1.

'L': Weak signal that should probably go to 0

Rappel à 0

- 'H': Weak signal that should probably go to 1 Rappel à 1

- Les opérations applicables à ce type sont : AND, NAND, OR, NOR, XOR, XNOR, NOT.

- Le type « std\_logic\_vector » est un tableau de « std\_logic ».

```

architecture Behavioral of portes is

signal s1, s2, s3 : std_logic_vector(3 downto 0);

begin

s1(0) <= '1';

s1(1) <= '0';

s1(2) <= '0';

s1(3) <= '1';

s2 <= "1100";

s3 <= s1 and s2;</pre>

18

```

18

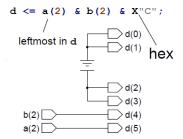

# AGRÉGATS (RÉUNIONS D'ÉLÉMENTS)

```

a : in std logic vector(2 downto 0);

b : in std_logic_vector(2 downto 0);

c : out std_logic_vector(5 downto 0);

d : out std_logic_vector(5 downto 0);

e : out std_logic_vector(5 downto 0);

f : out std logic vector(2 downto 0);

(MSB downto LSB)

index

leftmost in e

e <= (a(0), b(1), 0 => '1', others => '0');

(f(0), f(2), f(1)) \le a;

____ e(1)

____ e(2)

\geq e(3)

e(5)

MSB (Most Significant Bit) : bit de poids fort

19

LSB (Least Significant Bit) : bit de poids faible

```

# **CONCATÉNATION (BOUT À BOUT)**

```

a : in std_logic_vector(2 downto 0);

b : in std_logic_vector(2 downto 0);

c : out std_logic_vector(5 downto 0);

d : out std_logic_vector(5 downto 0);

e : out std_logic_vector(5 downto 0);

f : out std_logic_vector(2 downto 0);

```

20

20

#### LA FONCTION « RISING\_EDGE »

- Cette fonction, définie dans « std\_logic\_1164 », est très utile pour détecter les fronts montants d'une horloge.

- Elle vérifie bien que le signal part de '0' avant de passer à '1'.

- Il existe une fonction similaire qui teste les fronts descendants : « falling\_edge »

```

process (Clk, Reset)

begin

if Reset = '1' then

Q <= '0';

elsif rising_edge (Clk) then

Q <= D;

end if;

end process;

package std_logic_1164 is

...

function rising_edge (signal Clk: std_logic) return boolean;

begin

if (Clk'event and Clk= '1' and Clk'last_ value = '0') then

return true;

else

return false;

end if;

end rising edge;

...

```

21

#### 2.4.2. LE PACKAGE « NUMERIC\_STD »

C'est ici que sont définis certains types pour représenter les entiers ainsi que les opérations arithmétiques.

std logic

signed

std logic vector

unsigned

- The unsigned type

- The signed type

- The arithmetic functions: +, -, \*

- The comparison functions: <, <=, >, >=, =, /=

- The shift functions: shl, shr

- The conv\_integer function

- The conv unsigned function

- The conv\_signed function

- The conv std logic vector function

- On y trouve aussi quelques fonctions de conversion de type comme celle-ci :.

22

# STD\_LOGIC\_UNSIGNED / STD\_LOGIC\_SIGNED

- Ces deux packages sont des extensions du package « numeric\_std».

- Il ne faut appeler qu'un seul des deux à la fois !!!

#### STD LOGIC UNSIGNED:

Dans ce package, les fonctions sont redéfinies pour traiter les nombres de type « std\_logic\_vector » comme des entiers non signés.

#### STD LOGIC SIGNED:

- Dans ce package, les fonctions sont redéfinies pour traiter les nombres de type « std\_logic\_vector » comme des entiers signés.

- Le complément à 2 est utilisé pour la représentation des nombres négatifs.

```

library IEEE; -- librairie IEEE

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

use IEEE.std_logic_unsigned.all;

-- or IEEE.std_logic_signed.all;

```

23

#### 2.5. LE BLOC « ENTITY »

```

entity circuit is

Port (A: in STD_LOGIC;

B: in STD_LOGIC;

C: in STD_LOGIC;

X: out STD_LOGIC;

Y: out STD_LOGIC;

Y: out STD_LOGIC);

end circuit;

```

- L'entité donne une vue externe du circuit.

- Les signaux d'interface constituent dans la terminologie VHDL un « port ».

- Chaque signal doit posséder: un nom (choisi par l'utilisateur), un mode (in, out, inout) et un type (std\_logic, std\_logic\_vector, integer, boolean, ...).

- Dans le bloc entity, on peut déclarer un paramètre générique avec une valeur par défaut, si une architecture appelle cette entité elle pourra changer la valeur de N.

```

entity PARITE is

generic (N : integer := 8);

Port (ENTREE : in std_logic_vector(N-1 downto 0);

P : out std_logic);

end PARITE;

```

24

#### 2.6. LE CHOIX DES NOMS

- Chaque élément manipulé par VHDL (signal, constante, bus, ...) doit porter un nom.

Celui-ci doit respecter les règles suivantes :

- 1. Caractères admis : les 26 lettres de l'alphabet, les 10 chiffres décimaux et le caractère ' '.

- 2. Le 1er caractère doit être une lettre.

- 3. Le caractère '\_' ne doit pas terminer un nom.

- 4. Un nom ne doit pas être un mot réservé.

- 5. La longueur d'un nom ne doit pas dépasser une ligne.

Attention aux noms des fichiers, évitez les accents et caractères spéciaux  $\rightarrow$  des problèmes observés lors des simulations.

25

#### 2.7. LE BLOC « ARCHITECTURE »

- Le bloc architecture décrit le système matériel à concevoir, cela peut être un système combinatoire ou séquentiel, simple ou complexe.

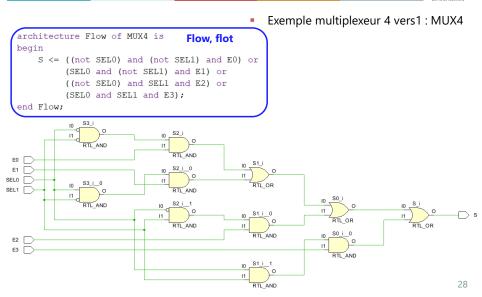

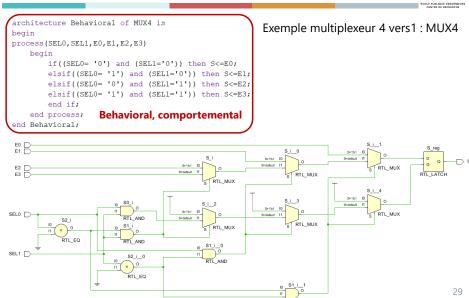

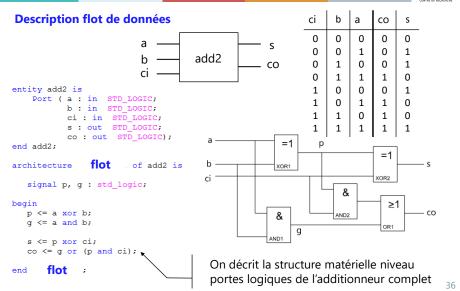

- Il existe trois façons de décrire un circuit électronique en VHDL :

- Description de bas niveau : on écrit des équations logiques :

- Flow, flot

- Description modulaire : il s'agit d'associer des blocs existants :

#### Structural, structurel

Description comportementale : on décrit le comportement du circuit :

#### Behavioral, comportemental

26

26

#### 2.7. LE BLOC « ARCHITECTURE »

SEL0

```

entity MUX4 is

E0

Exemple multiplexeur 4 vers1: MUX4

Port ( E0 : in STD_LOGIC;

El : in STD_LOGIC;

E1

- S

E2 : in STD_LOGIC;

E3 : in STD_LOGIC;

MUX4

F2

E3

SEL0 : in STD_LOGIC;

SEL1 : in STD_LOGIC;

architecture Behavioral of MUX4 is

S : out STD_LOGIC);

SELO SEL1

begin

end MUX4;

process (SELO, SEL1, EO, E1, E2, E3)

begin

if((SEL0= '0') and (SEL1='0')) then S<=E0;

architecture Flow of MUX4 is

Flow, flot

elsif((SELO= '1') and (SEL1='0')) then S<=E1;

elsif((SEL0= '0') and (SEL1='1')) then S<=E2;

S <= ((not SEL0) and (not SEL1) and E0) or

elsif((SEL0= '1') and (SEL1='1')) then S<=E3;

(SEL0 and (not SEL1) and E1) or

end if;

((not SEL0) and SEL1 and E2) or

(SELO and SEL1 and E3);

end process;

Behavioral, comportemental

end Behavioral;

architecture Structural of MUX4 is

Structural, structurel

component MUX2

MUX2

Port ( E0, E1, SEL : in STD_LOGIC; S : out STD_LOGIC);

end component;

signal S_MUX2_a, S_MUX2_b : STD_LOGIC;

SEL0

MUX2 - S

begin

instance_MUX2_a : MUX2 port map(E0=>E0, E1=>E1, SEL=>SEL0, S=>S_MUX2_a);

instance_MUX2_b : MUX2 port map(E0=>E2, E1=>E3, SEL=>SEL0, S=>S_MUX2_b);

MUX2

SEL1

instance_MUX2_c : MUX2 port map(E0=>S_MUX2_a, E1=>S_MUX2_b, SEL=>SEL1, S=>S);

27

end Structural;

```

## 2.7. LE BLOC « ARCHITECTURE »

28

#### 2.7. LE BLOC « ARCHITECTURE »

#### 2.7. LE BLOC « ARCHITECTURE »

30

# 2.8. DÉCLARATIONS / INSTRUCTIONS

```

architecture Behavioral of controle is

type etat_type is (zero, un, deux, trois, quatre, cinq);

signal etat : etat_type := zero;

signal etat_suiv : etat_type ;

signal compteur : std_logic_vector(26 downto 0) :=(others =>

Avant begin: déclaration

begin

Types

process(clk)

Signaux

begin

if rising_edge(clk) then

Variables

etat <= etat_suiv;

if (etat = un) then</pre>

composants

compteur <= compteur + 1;

end if;

if (etat = zero) then

compteur <= (others => '0');

end if;

end if;

Après begin : code

end process;

affectations

process(etat, compteur)

process

case etat is

when zero =>

valid <= '0';</pre>

verr <= '0';

raz <= '0';

etat_suiv <= un;

31

when un =>

```

#### 3.1. SYNTAXE HORS « PROCESS »

Affectation inconditionnelle

```

Y \ll A or B;

```

Affectation conditionnelle

```

Y <= A when sel="00" else

B when sel="01" else

C when sel="10" else

'0';</pre>

```

Y <= '1' when (SEL = "101") else '0';

Affectation sélective

32

32

#### 3.2. SYNTAXE DANS « PROCESS »

Affectation inconditionnelle

```

Y \ll A or B;

```

Affectation conditionnelle

```

if (SEL = "101") then

Y <= '1';

else

Y <= '0';

end if;</pre>

```

Ce qui ressemble à du langage C correspond à des instructions à l'intérieur de process

Affectation sélective

```

case sel is

when "00" => y <= '1';

when "01" => y <= '0';

when "10" => y <= '0';

when others => y <= '1';

end case;</pre>

```

33

#### 3.3. FONCTIONNEMENT CONCURRENT

- En dehors du PROCESS, toutes les instructions s'exécutent en parallèle. On parle de fonctionnement concurrent, c'est le principe des systèmes combinatoires.

- L'ordre des instructions n'a aucune importance.

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

OR2

entity concurrent is

Port ( C : in std_logic;

D : in std_logic;

E : in std_logic;

AND<sub>2</sub>

A : out std_logic);

end concurrent;

architecture Behavioral of concurrent is

signal B : std_logic;

begin

Ces deux solutions donnent le

A <= B OR C; -- solution

B <= D AND E; -- n° 1

même résultat après

compilation, c'est-à-dire le

-- B <= D AND E ; -- solution

-- A <= B OR C ; -- n° 2

schéma ci-dessus.

end Behavioral:

```

34

34

## 3.4. FONCTIONNEMENT SÉQUENTIEL

35

- Dans un « process », les instructions s 'exécutent de façon séquentielle.

- Le « process » s 'exécute à chaque changement d'état d 'un des signaux de la liste de sensibilité.

- La mise à jour des variables se fait au fur et à mesure que les instructions se déroulent.

- La mise à jour des signaux se fait à la fin du « process », après le « end ».

- Tous les « process » se déroulent en parallèle.

- L'ordre d'écriture des process n'a aucune importance.

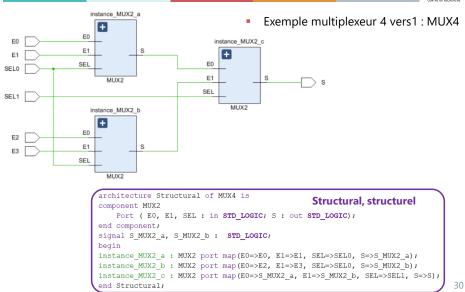

## 4.1. ADDITIONNEUR (1èRE FAÇON)

36

# 4.2. ADDITIONNEUR (2<sup>èME</sup> FAÇON)

# ci b a co s **Description comportementale** architecture Behavioral of add is signal co s : std\_logic\_vector (1 downto 0); signal ci\_b\_a : std\_logic\_vector (2 downto 0); ci\_b\_a <= ci & b & a; co <= co\_s (1); s <= co\_s (0);</pre> co\_s <= "00" when ci\_b\_a = "000" else "01" when ci\_b\_a = "001" else "01" when ci\_b\_a = "010" else "10" when ci\_b\_a = "011" else "01" when ci\_b\_a = "100" else "10" when ci\_b\_a = "101" else "10" when ci\_b\_a = "110" else "11" else "11" else end Behavioral:

| 0      | 0      | 0 | 0      | 0 |

|--------|--------|---|--------|---|

| 0      | 0      | 1 | 0      | 1 |

| 0      | 1      | 0 | 0      | 1 |

| 0      | 1<br>0 | 1 | 1<br>0 | 0 |

| 1      | 0      | 0 |        | 1 |

| 1      | 0      | 1 | 1      | 0 |

| 1<br>1 | 1<br>1 | 0 | 1<br>1 | 0 |

| 1      | 1      | 1 | 1      | 1 |

|        |        |   | •      |   |

On écrit la table de vérité des sorties de l'additionneur, l'outil de synthèse trouvera la logique nécessaire

37

## 4.3. ADDITIONNEUR (3<sup>èME</sup> FAÇON)

#### **Description comportementale**

```

architecture Behavioral of add2 is

begin

with ci & b & a select

s <= '0' when "000",

'1' when "001",

'1' when "010",

'0' when "011",

'1' when "100",

'0' when "101",

'0' when "110",

'1' when others;

with ci & b & a select

co <= '0' when "000",</pre>

'0' when "001",

'0' when "010",

'1' when "011",

'0' when "100",

'1' when "101",

'1' when "110",

'1' when others;

```

| ci | b | а | со | s |

|----|---|---|----|---|

| 0  | 0 | 0 | 0  | 0 |

| 0  | 0 | 1 | 0  | 1 |

| 0  | 1 | 0 | 0  | 1 |

| 0  | 1 | 1 | 1  | 0 |

| 1  | 0 | 0 | 0  | 1 |

| 1  | 0 | 1 | 1  | 0 |

| 1  | 1 | 0 | 1  | 0 |

| 1  | 1 | 1 | 1  | 1 |

Autre façon d'écrire les tables de vérité des sorties, une table par sortie cette fois.

end Behavioral;

38

38

# 4.4. ADDITIONNEUR (4<sup>èME</sup> FAÇON)

#### **Description comportementale**

```

architecture Behavioral of add is

signal co_s : std_logic_vector (1 downto 0);

signal ci_b_a : std_logic_vector (2 downto 0);

begin

process (ci_b_a) -- process (all) IEEE 2008

begin

case ci_b_a is

when "000" => co_s <= "00";

when "001" => co_s <= "01";

when "010" => co_s <= "01";

when "011" => co_s <= "10";

when "101" => co_s <= "10";

when "101" => co_s <= "10";

when "101" => co_s <= "11";

when "110" => co_s <= "11";

when others => co_s <= "11";

end case;

end process;

ci_b_a <= ci_& b_& a;

co <= co_s (1);

s <= co_s (0);

end Behavioral;</pre>

```

| 0         0         0         0         0           0         0         1         0         1           0         1         0         0         1           0         1         1         1         0           1         0         0         0         1 | ci |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                    | 0  |

| 0 1 1 1 0                                                                                                                                                                                                                                                 | 0  |

|                                                                                                                                                                                                                                                           | 0  |

| 1   0   0   0   1                                                                                                                                                                                                                                         | 0  |

|                                                                                                                                                                                                                                                           | 1  |

| 1 0 1 1 0                                                                                                                                                                                                                                                 | 1  |

| 1     1     0     1     0       1     1     1     1     1                                                                                                                                                                                                 | 1  |

| 1   1   1   1                                                                                                                                                                                                                                             | 1  |

Encore une table de vérité écrite cette fois dans un process. Rappelez-vous! La syntaxe n'est pas la même

39

## 4.4. ADDITIONNEUR (5<sup>èME</sup> FAÇON)

#### **Description structurelle**

```

architecture Structural_ADDI of addiStruct is

component PORTE_ET

port(E1, E2 : in STD_LOGIC; S : out STD_LOGIC);

end component;

component PORTE_XOR

port(E1, E2 : in STD_LOGIC; S : out STD_LOGIC);

end component PORTE_XOR

port(E1, E2 : in STD_LOGIC; S : out STD_LOGIC);

end component PORTE_OU

port(E1, E2 : in STD_LOGIC; S : out STD_LOGIC);

end component PORTE_OU

port(E1, E2 : in STD_LOGIC; S : out STD_LOGIC);

end component;

signal p, g, i : STD_LOGIC;

```

40

## 4.5. ADDITIONNEUR MOTS À 2 MOTS DE 2 BITS

#### **Description structurelle**

```

entity addI4bits is

Port ( a : in STD_LOGIC_VECTOR (1 downto 0);

b : in STD_LOGIC_VECTOR (1 downto 0);

s : out STD_LOGIC_VECTOR (1 downto 0);

cy : out STD_LOGIC);

end addI4bits ;

architecture structural of addI4bits is

COMPONENT add2

PORT(

a : IN std_logic;

b : IN std_logic;

ci : IN std_logic;

ci : IN std_logic;

co : OUT std_logic;

co : OUT std_logic;

signal c_sig : std_logic;

```

Fil pour relier la retenue de sortie c0 de l'additionneur de poids faible à la retenue d'entrée ci de l'additionneur de poids fort.

```

b_0

a_0

b

а

b

а

bit1

bit0

СО

ci

СО

ci

'0'

c_sig

s

s

S<sub>1</sub>

s_0

begin

bit0: add2 PORT MAP(

a => a(0),

b => b(0),

ci => '0',

s \Rightarrow s(0)

co => c_sig

bit1: add2 PORT MAP(

a => a(1),

b => b(1),

ci => c_sig

s \Rightarrow s(1),

co => cy

```

end structural; 41

## 4.6. ADDITIONNEUR MOTS À N BITS - BEH.

Voici un additionneur générique qui utilise l'opération arithmétique « + » du package « numeric\_std ».

Dans la pratique, constante N déclarée dans un package appelé pour rendre l'ensemble du code évolutif

43

43

## 4.6. ADDITIONNEUR MOTS À N BITS – STRUCT.

Additionneur générique structurel à partir d'un additionneur complet 1 bit.

```

entity Full_Adder is

port(

A,B,Ri: in std_logic;

S,R: out std_logic);

end Full_Adder;

architecture flot of Full_Adder is

signal somme_int: std_logic;

begin

somme_int <= A xor B;

S <= somme_int xor Ri;

R <= (A and B) or (somme_int or Ri);

end flot;</pre>

```

```

entity additionneur_Nbits is

generic (N: integer := 8);

port (Av, Bv : in std_logic_vector(N downto 1);

Ri : in std_logic;

Sv : out std_logic_vector(N downto 1);

R : out std_logic);

end additionneur_Nbits;

architecture structural of additionneur_Nbits is

component Full_Adder

port(A,B,Ri: in std_logic; S,R: out std_logic);

end component:

signal Cv : std_logic_vector(1 to N+1);

label_boucle_generation : for I in 1 to N generate

instance: Full\_Adder\ port\ map\ (Av(I),\ Bv(I),\ Cv(I),\ Sv(I),\ Cv(I+1));

end generate;

Cv(1) <= Ri;

R \leftarrow Cv(N+1);

end structural;

```

Code de l'additionneur complet 1 bit.

Code de l'additionneur N bit utilisant l'instruction generate.

#### 4.7. COMPTEUR À N BITS

```

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

use IEEE.std_logic_unsigned.all;

entity compteur1 is

generic (N : natural := 8); ← Variable générique

Port (clk : in STD_LOGIC;

count : out STD_LOGIC_VECTOR (N-1 downto 0));

end compteur1;

architecture Behavioral of compteur1 is

signal count_s : STD_LOGIC_VECTOR (N-1 downto 0);

Signal intermédiaire

process (clk) ←

Liste de sensibilité

if rising_edge(clk) then ←

——— Front montant

count_s <= count_s + 1;

end if;

end process;

count <= count_s; ← Connexion de la sortie

end Behavioral;

45

```

45

#### 4.8. COMPTEUR AVEC RESET ASYNCHRONE

46

#### 4.9. COMPTEUR AVEC RESET SYNCHRONE

```

entity compteur3 is

generic (N : natural := 8);

Port (clk: in STD_LOGIC; reset: in STD_LOGIC;

count : out STD_LOGIC_VECTOR (N-1 downto 0));

end compteur3;

architecture Behavioral of compteur3 is

signal count_s : STD_LOGIC_VECTOR (N-1 downto 0);

begin

process (clk) ←

Liste de sensibilité réduite

if rising_edge(clk) then

if reset='1' then

count_s <= (others => '0');

Front d'horloge prioritaire =

Reset synchrone

count_s <= count_s + 1;

end if;

end if;

end process;

count <= count_s;</pre>

```

47

47

#### 4.10. COMPTEUR AVEC VALIDATION

```

entity compteur4 is

generic (N : natural := 8);

Port ( clk : in STD_LOGIC;

reset : in STD_LOGIC;

ce : in STD_LOGIC;

count : out STD_LOGIC_VECTOR (N-1 downto 0));

end compteur4;

architecture Behavioral of compteur4 is

signal count_s : STD_LOGIC_VECTOR (N-1 downto 0);

begin

process (clk)

begin

if rising_edge(clk) then

if reset='1' then

« reset » prioritaire sur « ce »

count_s <= (others => '0');

elsif ce='1' then

« ce » valide le comptage

count_s <= count_s + 1;</pre>

else

count_s <= count_s; +

end if;

end if:

Pas de changement si ce = '0'

end process;

count <= count_s;

48

end Behavioral;

```

#### À PROPOS DU « RESET »

1ère règle : n'utiliser de signal « reset » que si cela est nécessaire !

- De toute façon, toutes les bascules sont remises à '0' à la mise sous tension.

- Les bénéfices sont les suivants :

- 1. Moins de logique générée par le compilateur.

- 2. Moins de problème au moment du routage.

49

49

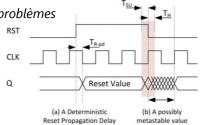

## À PROPOS DU « RESET »

Le « reset » asynchrone peut conduire à des problèmes

- Métastabilité des bascules (comportement non prédictible/non déterministe).

- Problèmes de fiabilité.

2ème règle : le signal « reset » doit être synchrone et local!

- La remise à zéro des bascules se fait au même moment sur front d'horloge comme les autres changements d'état.

- Pas de reset global pour éviter les effets des retards différents d'une bascule à l'autre.

50

#### 4.11. DÉCODEUR 2 VERS 4

Système combinatoire décrit hors « process » en utilisant la structure « when ... else »

53

53

#### 4.12. MULTIPLEXEUR

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

a ·

use IEEE.STD LOGIC ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

sortie

C

entity multipexe is

Port (a: in std_logic;

b: in std_logic;

c: in std_logic;

d: in std_logic;

sel: in std_logic vector(1 downto 0);

sel(1) sel(0)

sortie : out std_logic);

end multipexe;

architecture Behavioral of multipexe is

begin

sortie <= a when sel = "00" else

b when sel = "01" else

c when sel = "10" else

d when sel = "11" else

'X';

end Behavioral;

```

Système combinatoire décrit hors « process » en utilisant la structure « when ... else »

54

#### 4.13. DÉCODEUR HEXA VERS 7 SEGMENTS

```

entity hex2led is

Port ( HEX : in std_logic_vector(3 downto 0);

LED : out std_logic_vector(6 downto 0));

end hex2led;

architecture Behavioral of hex2led is

begin

with HEX SELect

With HEX SELect

LED<= "1111001" when "0001",

"0100100" when "0010",

"0110000" when "0011",

"0011001" when "0100",

--3

"0010010" when "0101",

"0000010" when "0110",

"1111000" when "0111",

"0010010" when

--6

"0000000" when

"1000",

"0010000" when "1000",

"0010000" when "1001",

"0001000" when "1010",

"0000011" when "1011",

"1000110" when "1100",

--b

--c

"01000110" when "1100",

"0100001" when "1101",

"0000110" when "1110",

--E

"0001110" when "1111",

"1000000" when others;

end Behavioral;

```

Système combinatoire décrit hors « process » en utilisant la structure « with ... select ». C'est une façon d'écrire la table de vérité.

55

55

## 4.14. ENCODEUR DE PRIORITÉ

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity encodeur is

Port (entree: in std_logic_vector(3 downto 0);

sortie: out std_logic_vector(1 downto 0));

end encodeur;

architecture Behavioral of encodeur is

begin

process (entree)

begin

if entree(3)='1' then sortie<="11";

elsif entree(2)='1' then sortie<="10";

elsif entree(1)='1' then sortie<="01";

elsif entree(0)='1' then sortie<="00";

else sortie<="XX";

end if;</pre>

end process;

end Behavioral;

```

Système combinatoire décrit dans un « process » en utilisant la structure « if... then ... else ». On peut décrire une fonction combinatoire dans un « process »

56

## 4.15. CALCUL DU BIT DE PARITÉ

```

entity parite is

Port ( mot : in std_logic_vector(7 downto 0);

parite : out std_logic);

end parite;

architecture Behavioral of parite is

begin

process (mot)

variable x : std logic;

begin

Exemple d'utilisation de

x := '0';

l'instruction for

for i in 0 to 7 loop

if mot(i) = '1' then

(uniquement dans un process)

x := not x;

end if;

end loop;

parite <= x;

end process;

end Behavioral;

```

Système combinatoire décrit dans un « process » en utilisant la structure « for... loop ».

57

57

#### 4.16. DIVISEUR D'HORLOGE PAR 2<sup>N</sup>

```

entity clk_div is

generic (N : natural := 5);

div_out : out STD_LOGIC);

end clk_div;

architecture Behavioral of clk_div is

signal count_temp : std_logic_vector(N-1 downto 0);

begin

process (clk)

begin

if rising_edge (clk) then

if (reset = '1') then

count_temp <= (others => '0');

count_temp <= count_temp + 1;</pre>

end if;

end if;

end process;

div_out <= count_temp(N-1);</pre>

end Behavioral;

```

La division d'une fréquence se fait toujours avec un compteur synchrone.

58

#### 4.17.1. CONVERSION BINAIRE VERS BCD

- L'algorithme de conversion utilise le fait que tous les chiffres compris entre 0 et 4 produisent un résultat sur un chiffre lorsqu'ils sont multipliés par 2.

- Par contre tous les chiffres compris entre 5 et 9 donnent un résultat sur 2 chiffres lorsqu'ils sont multipliés par 2.

| chiffre | Chiffre*2 | dizaines | unités |

|---------|-----------|----------|--------|

| 0       | 0         | 0        | 0      |

| 1       | 2         | 0        | 2      |

| 2       | 4         | 0        | 4      |

| 3       | 6         | 0        | 6      |

| 4       | 8         | 0        | 8      |

| 5       | 10        | 1        | 0      |

| 6       | 12        | 1        | 2      |

| 7       | 14        | 1        | 4      |

| 8       | 16        | 1        | 6      |

| 9       | 18        | 1        | 8      |

59

59

#### 4.17.2. APPLICATION DE L'ALGORITHME

$0 \le nb \le 4$

En décimal :

| Nb | Nb*2 |

|----|------|

| 0  | 0    |

| 1  | 2    |

| 2  | 4    |

| 3  | 6    |

| 4  | 8    |

En BCD : un décalage à gauche

|      | . 0 0 |

|------|-------|

| Nb   | Nb*2  |

| 0000 | 0000  |

| 0001 | 0010  |

| 0010 | 0100  |

| 0011 | 0110  |

| 0100 | 1000  |

$5 \le nb \le 9$

Exemple en décimal :  $2 \times 6 = 12$

En BCD : ajouter 3 et décaler à

gauche

|    | diz  | uni  |

|----|------|------|

| 6  | 0000 | 0110 |

| +3 | 0000 | 0011 |

| =  | 0000 | 1001 |

| X2 | 0001 | 0010 |

#### 4.17.3. ALGORITHME COMPLET

- Déclarer un registre de 20 bits : 4 + 4 + 4 + 8

- Les 8 bits de poids faible représentent le mot binaire à convertir

- Suivent ensuite 3 quartets dans l'ordre : les unités, les dizaines puis les centaines du résultat en BCD

#### Réaliser les étapes suivantes 8 fois

- 1. Si les unités sont ≥5 , ajouter 3. Faire la même chose pour les dizaines et les centaines

- 2. Décaler tout le registre d'un bit vers la gauche

| Operation | Hundreds | Tens | Units | Binary |   |   |   |   |   |   |   |

|-----------|----------|------|-------|--------|---|---|---|---|---|---|---|

| HEX       |          |      |       | F      |   |   |   | F |   |   |   |

| Start     |          |      |       | 1      | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

61

61

# 4.17.4A. CONVERSION D'UN MOTS À 8 BITS

|          |           |      |      |           | Mot binaire |      |   |

|----------|-----------|------|------|-----------|-------------|------|---|

| décalage | Opération | CENT | DIZ  | UNI       | 7654        | 3210 |   |

|          | START     | 0000 | 0000 | 0000      | 1111        | 1111 |   |

| 1        | SHIFT     | 0000 | 0000 | 0001      | 1111        | 1110 |   |

| 2        | SHIFT     | 0000 | 0000 | 0011      | 1111        | 1100 |   |

| 3        | SHIFT     | 0000 | 0000 | 0111      | 1111        | 1000 |   |

|          | + 3       | 0000 | 0000 | 1010      | 1111        | 1000 | ] |

| 4        | SHIFT     | 0000 | 0001 | 0001 0101 |             | 0000 | 1 |

|          | + 3       | 0000 | 0001 | 1000      | 1111        | 0000 | 1 |

| 5        | SHIFT     | 0000 | 0011 | 0001      | 1110        | 0000 | 1 |

| 6        | SHIFT     | 0000 | 0110 | 0011      | 1100        | 0000 | ] |

|          | + 3       | 0000 | 1001 | 0011      | 1100        | 0000 | ] |

| 7        | SHIFT     | 0001 | 0010 | 0111      | 1000        | 0000 | 1 |

|          | + 3       | 0001 | 0010 | 1010      | 1000        | 0000 |   |

| 8        | SHIFT     | 0010 | 0101 | 0101      | 0000        | 0000 |   |

|          |           | 2    | 5    | 5         |             |      | 6 |

#### 4.17.4B. CONVERSION D'UN MOTS À 8 BITS

|          |           |      |           |      | Mot binaire |      |  |

|----------|-----------|------|-----------|------|-------------|------|--|

| décalage | Opération | CENT | DIZ       | UNI  | 7654        | 3210 |  |

|          | START     | 0000 | 0000      | 0000 | 0000        | 1100 |  |

| 1        | SHIFT     | 0000 | 0000      | 0000 | 0001        | 1000 |  |

| 2        | SHIFT     | 0000 | 0000      | 0000 | 0011        | 0000 |  |

| 3        | SHIFT     | 0000 | 0000      | 0000 | 0110        | 0000 |  |

| 4        | SHIFT     | 0000 | 0000      | 0000 | 1100        | 0000 |  |

| 5        | SHIFT     | 0000 | 0000 0001 |      | 1000        | 0000 |  |

| 6        | SHIFT     | 0000 | 0000      | 0011 | 0000        | 0000 |  |

| 7        | SHIFT     | 0000 | 0000      | 0110 | 0000        | 0000 |  |

|          | +3 0000   |      | 0000      | 1001 | 0000        | 0000 |  |

| 8        | SHIFT     | 0000 | 0001      | 0010 | 0000        | 0000 |  |

|          |           | 0    | 1         | 2    |             |      |  |

63

63

#### 4.17.5. CODE VHDL (BINAIRE VERS BCD)

```

process (binaire)

variable registre : std_logic_vector(19 downto 0);

begin

registre := x"000" & binaire;

-- registre de travail

for i in 1 to 8 loop

registre(11 downto 8) := registre(11 downto 8) + 3;

if registre(15 downto 12) > 4 then -- dizaines

registre (15 downto 12) := registre (15 downto 12) + 3;

end if;

if registre(19 downto 16) > 4 then -- unités

registre(19 downto 16) := registre(19 downto 16) + 3;

end if;

registre := registre(18 downto 0) & '0'; -- décalage G

end loop;

cent <= registre(19 downto 16); -- sorties décimales

diz <= registre(15 downto 12);

uni <= registre(11 downto 8);

end process;

```

64

64

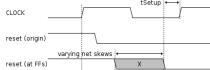

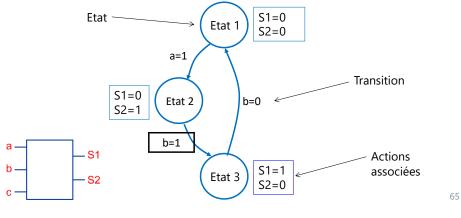

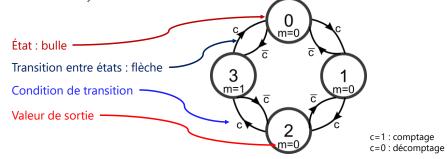

#### 5.1. MACHINE D'ÉTATS

- Une machine d'états est un séquenceur qui décrit le fonctionnement d'un système séquentiel aussi complexe soit-il.

- On utilise des symboles: les bulles indiquent les états du système et les arcs orientés définissent les possibilités d'évolution. Le passage d'un état à un autre est régi par une condition (transition). Les sorties dépendent de l'état présent.

65

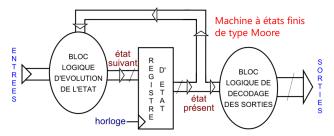

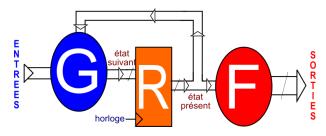

## 5.2. MACHINE À ÉTATS FINIS

67

Structure séquentielle pour réaliser des automates ou compteurs (le compteur est un cas d'automate simple). Une machine d'état est un opérateur séquentiel dont la sortie est fonction des entrées et de l'état précédent de la machine d'état. Elle utilise des bascules pour mémoriser l'état présent et des blocs de logique combinatoire pour générer les sorties et l'état futur. La machine d'état permet l'implémentation de diagrammes d'état décrivant des systèmes séquentiels.

Le type Moore garantit des **signaux logiques synchrones**. Il est privilégié dans les applications intégrées et cœur de calculateur pour la réalisation de séquenceur. Les sorties dépendent exclusivement de l'état

#### 5.2. MACHINE À ÉTATS FINIS

Diagrammes d'états: représentation symbolique d'un système séquentiel. Il s'agit d'un outil graphique utilisé pour modéliser le comportement d'un système séquentiel en représentant ses différents états et les transitions entre ces états en fonction des entrées et des conditions. Il permet de décrire comment un système évolue au fil du temps, ce qui est essentiel pour la synthèse et la conception de circuits séquentiels comme les machines à états finis. Ce diagramme facilite la conception logique en offrant une vision claire des interactions entre les différents états du système.

Diagramme d'état d'un compteur-décompteur 4 états avec sortie à 1 pour la valeur maximum

68

69

## 5.2. MACHINE À ÉTATS FINIS

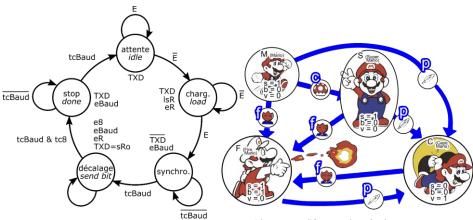

Exemples de diagrammes d'états.

Diagramme d'état de la machine à états finis de contrôle de l'interface UART

Diagramme d'état : notion plus large que l'électronique numérique, adaptée aux systèmes séquentiels, à la programmation.

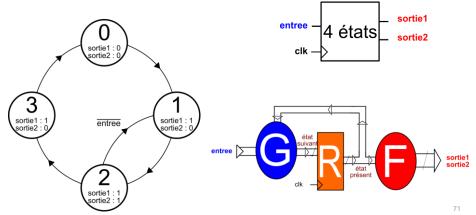

#### 5.2. MAEF EN VHDL

- 4 façons de coder une machine d'état de type Moore

- 3 processus: 1 pour chaque bloc logique G, R et F

- 2 processus: (G+R) et F ou R et (G+F)

- 1 processus: G+R+F

G: bloc logique combinatoire d'évolution des états (prépare l'état suivant)

R: registre d'état (mémorise l'état)

F : bloc logique de décodage des sorties (évalue les sorties en fonction de l'état présent)

70

70

#### 5.2. MAEF EN VHDL: SUR UN EXEMPLE

Diagramme d'état et schéma bloc de l'exemple

Machine 4 états, 1 entrée, 2 sorties

72

72

#### 5.2. MAEF EN VHDL: SUR UN EXEMPLE

## **3 PROCESSUS (PROCESS)**

```

architecture Behavioral_3p of MAEF3p is

type type_etat is (etat0, etat1, etat2, etat3);

signal etat_present: type_etat;

signal etat_suivant: type_etat;

Définition d'un type état pour la clarté du code.

Dans ce cas, on a besoin de définir deux signaux du type état

etat_present et etat_suivant

pbegin

· bloc logique combinatoire décodade des sorties

-- pour la synthèse du registre d'état

PROC_SEQ : process(clk)

COMB_F : process(etat_present)

begin

begin

case etat_present is

when etat0 => sortie1 <= '0'; sortie2 <= '0'

when etat1 => sortie1 <= '1'; sortie2 <= '1'

when etat2 => sortie1 <= '1'; sortie2 <= '1'

when etat3 => sortie1 <= '1'; sortie2 <= '0'</pre>

if rising_edge(clk) then

-- changement d'état sur front d'horloge

| etat_present <= etat_suivant;</pre>

end if;

end process PROC_SEQ;

end case;

end process COMB_F;

--- bloc logique combinatoire évolution des états

COMB_G : process(etat_present, entree)

end Behavioral_3p;

begin

case etat_present is

when etat0 => etat_suivant <= etat1;

when etat1 => etat_suivant <= etat2;

when etat2 => if entree = '1' then

etat_suivant <= etat3;

else</pre>

etat_suivant <= etat1;

end if;

when etat3 => etat_suivant <= etat0;</pre>

end case;

d process COMB_G;

```

73

#### 2 PROCESSUS (PROCESS) G+R ET F

```

-- 2 process Evolution+registre d'état et décodage sorties

architecture Behavioral 2p of MAEFZp is

type type_etat is (etat0, etat1, etat2, etat3);

signal etat : type_etat;

Définition d'un type état pour la clarté du

code.

Dans ce cas, un seul signal du type état.

begin

- pour la synthèse du registre d'état et du

-- bloc logique d'évolution des états

PROC_ETAT : process(clk)

case etat is

e etat 1s

when etat0 => sortie1 <= '0'; sortie2 <= '0';

when etat1 => sortie1 <= '1'; sortie2 <= '1';

when etat2 => sortie1 <= '1'; sortie2 <= '1';

when etat3 => sortie1 <= '1'; sortie2 <= '0';</pre>

begin

if rising edge(clk) then

case etat is

when etat0 => etat <= etat1;</pre>

when etat1 => etat <= etat2;

when etat2 => if entree = '1' then

etat4 <= etat3;

end process COMB F:

end Behavioral 2p;

else

etat <= etat1;

end if;</pre>

when etat3 => etat <= etat0;</pre>

end case;

end if:

nd process PROC_ETAT;

74

```

74

#### 5.2. MAEF EN VHDL: SUR UN EXEMPLE

75

## 2 PROCESSUS (PROCESS) R ET G+F

```

Définition d'un type état pour la clarté du code.

-- 2 process registre d'état et blocs logiques

-- (évolution états+décodage sorties)

Dans ce cas, on a besoin de définir deux signaux

Garchitecture Behavioral 2pV2 of MAEF2pV2 is

type type_etat is (etat0, etat1, etat2, etat3);

du type état etat_present et etat_suivant

signal etat_present : type_etat;

signal etat_suivant : type_etat;

- pour la synthèse des blocs logiques combinatoires

-- (état suivant et décodage sorties)

COMB_F_G : process(etat_present, entree)

begin

begin

-- pour la synthèse du registre d'état

PROC_SEQ : process(clk)

case etat present is

when etat0 => sortie1 <= '0'; sortie2 <= '0';</pre>

if rising_edge(clk) then

-- changement d'état sur front d'horloge

etat_present <= etat_suivant;</pre>

end process PROC SEQ;

else

else

etat_suivant <= etat1;

end if;

when etat3 => sortie1 <= '1'; sortie2 <= '0';

etat_suivant <= etat0;</pre>

end case:

end process COMB F G;

end Behavioral 2pV2;

```

75

#### 1 PROCESSUS (PROCESS) G+R+F

76

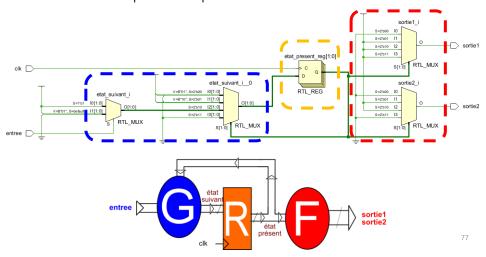

#### 5.2. MAEF EN VHDL: SUR UN EXEMPLE

#### SYNTHÈSE RTL

Les solutions 3 process et 2 process conduisent à la même structure.

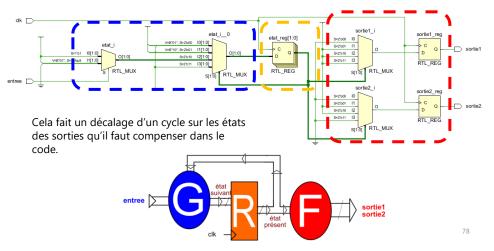

## SYNTHÈSE RTL

La solution 1 process conduit à une structure avec des bascules sur les sorties.

78

## 5.2. MAEF EN VHDL: SUR UN EXEMPLE

# Social: 1 social

## **SIMULATION**

• Résultats de simulation équivalents

|        | Name                               | Malian |         |     |       |      |       |        |       |         |       |      |       | `    | $\smile$ |       |       |

|--------|------------------------------------|--------|---------|-----|-------|------|-------|--------|-------|---------|-------|------|-------|------|----------|-------|-------|

|        | Name                               | Value  | 0 ns    |     | 10 ns | Line | 20 ns | ليبينا | 30 ns | التنبيا | 40 ns | Line | 50 ns | Line | 60 ns    | Line  | 70 ns |

|        | ¼ clk                              | 1      |         |     |       |      |       |        |       |         |       |      |       |      |          |       |       |

|        | ¹a entree                          | 0      |         |     |       |      |       |        |       |         |       |      |       |      |          |       |       |

| SS     | ⅓ /MAEF_tb/u_maef3p/etat_present   | etat1  | etat0   | ets | t1    | eti  | ıt2   | eta    | t3    | ets     | t0    | eti  | t1    | et   | at2      | et    | tl    |

| ő      | MAEF_tb/u_maef3p/etat_suivant      | etat2  | etatl   | eti | t2    | eti  | ıt3   | eta    | t0    | eta     | t1    | eti  | ıt2   | et   | atl      | et    | t2    |

| ā      | Im /MAEF_tb/u_maef3p/sortie1       | 1      |         |     |       |      |       |        |       |         |       |      |       |      |          |       |       |

| m      | Im /MAEF_tb/u_maef3p/sortie2       | 1      |         |     |       |      |       |        |       |         |       |      |       |      |          |       |       |

|        | MAEF_tb/u_maef2p/etat              | etat1  | etat0   | eta | t1    | eti  | t2    | eta    | t3    | eta     | t0    | eta  | tl    | et   | at2      | ) et: | t1    |

| S      | Im/MAEF_tb/u_maef2p/sortie1        | 1      |         |     |       |      |       |        |       |         |       |      |       |      |          |       |       |

| ces    | In /MAEF_tb/u_maef2p/sortie2       | 1      |         |     |       |      |       |        |       |         |       |      |       |      |          |       |       |

| e<br>e | ⅓ /MAEF_tb/u_maef2pV2/etat_present | etat1  | etat0   | eta | t1    | eta  | it2   | ets    | it3   | ( eta   | t0    | eti  | tl    | et   | at2      | et:   | tl    |

| 7      | 4 /MAEF_tb/u_maef2pV2/etat_suivant | etat2  | etatl   | eta | t2    | ( et | it3   | ets    | t0    | eta     | tl    | eti  | t2    | et   | atl      | X et: | t2    |

|        | Im /MAEF_tb/u_maef2pV2/sortie1     | 1      |         |     |       |      |       |        |       |         |       |      |       |      |          |       |       |

|        | Im /MAEF_tb/u_maef2pV2/sortie2     | 1      |         |     |       |      |       |        |       |         |       |      |       |      |          |       |       |

| ess    | ⅓ /MAEF_tb/u_maef1p/etat           | etat1  | (etat0) | eta | t1    | ( et | t2    | eta    | t3    | ) eta   | t0    | eti  | tl    | ) et | at2      | ( et: | tl    |

| ĕ      | 1 /MAEF_tb/u_maef1p/sortie1        | 1      |         |     |       |      |       |        |       |         |       |      |       |      |          |       |       |

| 4      | Im /MAEF_tb/u_maef1p/sortie2       | 1      |         |     |       |      |       |        |       |         |       |      |       |      |          |       |       |

79

#### **QUELLE SOLUTION CHOISIR?**

Toutes les solutions sont fonctionnelles.

- Les électroniciens utilisent plutôt les solutions 3 ou 2 process. Solutions plus proches du matériel.

- En phase d'apprentissage, privilégiez les solutions 3 ou 2 process. Code plus lisible, plus structuré.

- Des informaticiens plutôt une solution 1 process.

- Attention à la gestion des sorties à cause des bascules dans ce cas.

80

80

#### 6.1. PRINCIPE DU « TESTBENCH »

- ☐ Tester un circuit revient à lui imposer des signaux en entrée « stimuli » et à regarder comment évoluent les sorties. Si les réponses correspondent à ce que l'on attend, le test est bon, sinon il y a erreur.

- Le « testbench » est un programme VHDL qui réalise toutes ces opérations .

TESTEUR 81

#### 6.2. CIRCUIT COMBINATOIRE À TESTER

Nous avons affaire à un circuit combinatoire à 3 entrées et 2 sorties, il s'agit d'un additionneur complet.

82

82

## 6.3. TESTBENCH: DÉCLARATIONS

```

ENTITY additionneur1_testeur_vhd_tb IS

END additionneur1_testeur_vhd_tb;

ARCHITECTURE behavior OF additionneur1_testeur_vhd_tb IS

COMPONENT additionneur1

PORT(

a : IN std_logic;

b : IN std_logic;

retenue_e : IN std_logic;

somme : OUT std_logic;

retenue_s : OUT std_logic;

retenue_s : ouT std_logic;

SIGNAL a : std_logic;

SIGNAL b : std_logic;

SIGNAL retenue_e : std_logic;

SIGNAL retenue_e : std_logic;

SIGNAL retenue_s : std_logic;

SIGNAL retenue_s : std_logic;

SIGNAL retenue_s : std_logic;

```

En début de programme, on déclare le composant à tester ainsi que les différents signaux qui vont servir à connecter le composant.

83

## **6.4. TESTBENCH: SIMULATION**

```

uut: additionneur1 PORT MAP(

a => a,

b => b,

retenue_e => retenue_e,

somme => somme,

retenue_s => retenue_s

);

tb : PROCESS

BEGIN

a<='0'; b<='0'; retenue_e<='0';

wait for 100 ns;

a<='1';

wait for 100 ns;

b<='1';

wait for 200 ns;

retenue_e<='1';

wait for 100 ns;

a<='0'; b<='0';

END PROCESS;</pre>

```

La fin du programme sert à connecter le composant et lui imposer des « stimuli » en entrée pour savoir comment il réagit.

84

84

## 6.5. CIRCUIT SÉQUENTIEL À TESTER

Il s'agit de simuler un diviseur de fréquence par 8 qui utilise un compteur binaire sur 3 bits.

85

## 6.6. TESTBENCH: DÉCLARATIONS

```

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

ENTITY diviseur_testeur2_vhd_tb IS

END diviseur_testeur2_vhd_tb;

ARCHITECTURE behavior OF diviseur_testeur2_vhd_tb IS

COMPONENT diviseur

PORT(

reset : IN std_logic;

clk : IN std_logic;

sortie : OUT std_logic

);

END COMPONENT;

SIGNAL reset : std_logic;

SIGNAL sortie : std_logic;

SIGNAL sortie : std_logic;

```

En début de programme, on déclare le composant à tester ainsi que les différents signaux qui vont servir à connecter le composant.

86

86

#### 6.7. TESTBENCH: SIMULATION

BEGIN

```

uut: diviseur PORT MAP(

reset => reset,

clk => clk,

sortie => sortie );

horloge : PROCESS

BEGIN

clk <= '0';

wait for 10 ns;

clk <= '1';

wait for 10 ns;

END PROCESS;</pre>

```

raz : PROCESS

BEGIN

reset <= '1';

wait for 15 ns;

reset <= '0';

wait for 40 ns;

reset <= '1';

wait;

END PROCESS;</pre>

END;

La fin du programme sert à connecter le composant et lui imposer des « stimuli » en entrée pour savoir comment il réagit.

87

#### 6.8. CONTRÔLE DES RÉSULTATS

```

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

reset <= '1';

sig <= '0';

wait for clk_period*5;

reset <= '0';</pre>

wait for 120ns;

sig <= '1';

wait for clk_period*10;

assert sig_mef = '0'

-- teste si sig_mef = '0' sinon

report "La valeur de sig_mef est fausse " -- afficher ce message

severity FAILURE;

-- et abandonner la simulation

wait for clk_period*65535;

end process;

```

- Assert ...

- Report ...

- Severity ...

88

## 6.9. TESTER DIFFÉRENTES CONFIGURATIONS

88

```

LIBRARY work;

Déclaration dans un fichier

de configuration séparé, ou

CONFIGURATION Projet_cfg OF Projet IS

bien dans le testbench.

FOR schematic

FOR OTHERS: add16

Ici, nom de l'architecture

USE ENTITY work.add16(beh_Ripple);

que l'on choisit pour la

END FOR

simulation.

FOR OTHERS: mult16

USE ENTITY work.mult16(beh_Wallace);

END FOR;

END FOR;

END Projet_cfg;

```

89

## 6.9. TESTER DIFFÉRENTES CONFIGURATIONS

```

entity ex config addi2 is

Port (A, B, Ri : in STD_LOGIC; S, R : out STD_LOGIC);

end ex_config_addi2;

architecture Architectural_ADDI of ex_config_addi2 is

component DEMI_ADDI

port(A, B : in STD_LOGIC; S, R : out STD_LOGIC);

end component;

component PORTE OU

port(E1, E2 : in STD_LOGIC; Z : out STD_LOGIC);

end component;

≥1

signal S1, S2, S3 : STD_LOGIC;

spécification de configuration

S

C_{o}

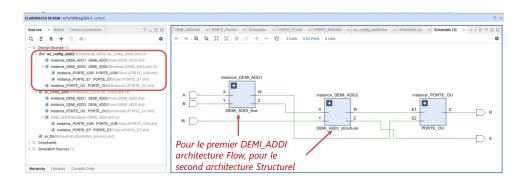

for instance_DEMI_ADD1 : DEMI_ADDI use entity work.DEMI_ADDI(Flow)

port map (X=>A, Y=>B, Z=>S, W=>R);

for instance_DEMI_ADD2 : DEMI_ADDI use entity work.DEMI_ADDI(Structurel)

port map (X=>A, Y=>B, Z=>S, W=>R);

begin

Pour le premier DEMI_ADDI

instance_DEMI_ADD1 : DEMI_ADD1 port map(A=>A,B=>B,S=>S1,R=>S2);

architecture Flow, pour le

instance_DEMI_ADD2 : DEMI_ADDI port map(A=>S1,B=>Ri,S=>S,R=>S3);

second architecture Structurel

instance_PORTE_OU : PORTE_OU port map(E1=>S3,E2=>S2,Z=>R);

end Architectural ADDI;

```

90

90

## 6.9. TESTER DIFFÉRENTES CONFIGURATIONS

**Swd**

Dans ce cas, pas d'intérêt particulier de mêler 2 architectures différentes. Il s'agit d'un exemple pour illustrer la syntaxe. Pour utiliser la même configuration pour les 2 modules DEMI\_ADDI, on utilise l'instruction for all. -- spécification de configuration

```

for all : DEMI_ADDI use entity work.DEMI_ADDI(Flow)

port map(X=>A,Y=>B,Z=>S,W=>R);

```

91