## 3A ELEC FISE - SATE

## ARCHITECTURES POUR LE CALCUL

## TRAVAUX PRATIQUES

### ARCHITECTURES POUR LE CALCUL

### CONTACTS

hugo descoubes hugo.descoubes@ensicaen.fr +33 (0)2 31 45 27 61

Isabelle Lartigau isabelle.lartigau@ensicaen.fr

Emmanuel Cagniot emmanuel.cagniot@ensicaen.fr

ENSICAEN 6 boulevard Maréchal Juin CS 45053 14050 CAEN cedex 04

### RESSOURCES

Les différentes ressources numériques sont accessibles sur la plateforme pédagogique de l'ENSICAEN. Télécharger l'archive complète de travail dsp.zip

https://foad.ensicaen.fr/course/view.php?id=117

## ENSI CAEN

## ARCHITECTURES POUR LE CALCUL

## ÉVALUATION

Examen de pratique sur ordinateur (1h30)

L'évaluation de la compétence se fera sur machine personnelle ou machine école et portera sur les points suivants :

- Création d'un projet sous IDE CCS. A l'image du projet présent dans cm/eval/examen\_nom

- Optimisation d'une fonction algorithmique élémentaire (cf. trame de TP)

- écriture en C canonique

- écriture ASM C6000 canonique

- écriture ASM VLIW

- écriture de l'algorithme optimisé avec l'une des techniques avancée suivante :

- Vectorisation en langage C par programmation intrinsèque

- Pipelining software en ASM C6000

- Vectorisation en base 2 ou 4 en ASM C6000

# ©creative (©©

# TRAVAUX PRATIQUES

PRÉLUDE

### SOMMAIRE

La trame de TP minimale que nous considérons comme être les compétences minimales à acquérir afin d'accéder aux métiers de base du domaine suit le séquencement suivant : chapitres 1, 2 et 3. Le reste de la trame ne sera pas évalué et représente une extension au jeu de compétences minimales relatif au domaine en cours d'étude (\* devant chapitres facultatifs voire complémentaires). Libre à vous d'aller plus loin selon votre temps disponible et votre volonté de mieux comprendre et maîtriser ce domaine!

### 1. PRÉLUDE

- 1.1. Optimisation algorithmique

- 1.2. Convolution discrète ou filtre FIR

- 1.3. Exemple des applications Radar

- 1.4. Architecture DSP VLIW C6600 de TI

- 1.5. Outils de développement

- 1.6. Objectifs pédagogiques

- 1.7. Benchmarking

#### 2. PROGRAMMATION VECTORIELLE SUR DSP VLIW C6600

- 2.1. Création du projet de test

- 2.2. Analyse du programme de test

- 2.3. Assembleur canonique C6600

- 2.4. Assembleur VLIW C6600

- 2.5. Pipelining software en assembleur C6600

- 2.6. Vectorisation d'algorithme en assembleur C6600

- 2.7. Déroulement de boucle en C canonique

- 2.8. Vectorisation d'algorithme en C intrinsèque

### 3. PROGRAMMATION VECTORIELLE SUR GPP INTEL x86 64

- 3.1. Analyse du programme de test

- 3.2. Vectorisation avec ISA extension SSE4.1

- 3.3. Synthèse

### \*4. MÉMOIRE CACHE ET MÉMOIRE SRAM ADRESSABLE

- 4.1. Mémoire locale SRAM adressable

- 4.2. Préchargement des données de DDR DRAM vers L2 SRAM

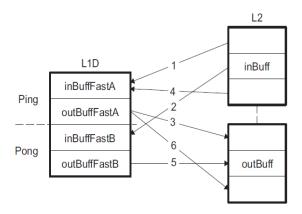

- 4.3. Préchargement des données de L2 SRAM vers L1D SRAM

### \*5. PÉRIPHÉRIQUES DE COPIE MÉMOIRE DMA

- 5.1. Transferts par IDMA

- 5.2. Stratégie Ping Pong

- 5.3. Transferts par EDMA

### SEQUENCEMENT

Le séquencement de la trame de Travaux Pratiques correspond au chemin proposé afin d'atteindre les objectifs pédagogiques fixés. Ces objectifs ont été choisis au regard des attentes et exigences demandées par les marchés de l'industrie du logiciel et des couches basses des systèmes : systèmes embarqués, systèmes temps réel, développement de systèmes d'exploitation, développement de bibliothèques spécialisées, développement de chaînes de compilation, attaque et sécurité des systèmes, etc, tous des métiers dans divers domaines actuellement exercés par certains de nos anciens élèves. Il s'agit d'un séquencement conseillé qui n'a en aucune façon volonté à être imposé (étudiant comme enseignant encadrant). Pour se dérouler sous les meilleurs hospices, il serait cependant préférable dès le début de l'enseignement de rythmer 1 à 2 heures par semaine de travail personnel à la maison en dehors des séances en présentiel avec enseignant. Voici une proposition de séquencement (2h par créneau de TP) :

- Avant le début des TP : Lire le document de prélude, installer les outils de développement (IDE CCS 5.5, bibliothèques CSL et DSPLIB), valider l'exercice 2.1 (projet hello seulement) et faire le travail préparatoire n°1 (dsp-tp-preparations.pdf)

- Séance n°1: Exercices 2.1 et 2.2

- Séance n°2 : Exercice 2.3 et 2.4 (avant la séance, faire le travail préparatoire n°2)

- Séance n°3 : Exercice 2.5

- Séance n°4 : Exercice 2.6

- Séance n°5 : Exercice 2.7

- Séance n°6 : Exercice 2.8

- Séance n°7: Exercices 3.1 et 3.2

- Séance n°8 : Exercice 4.1 et 4.2 (avant la séance, faire le travail préparatoire n°4)

- Séance n°9 : Exercice 4.3

- Séance n°10 : Exercice 5.1, etc (avant la séance, faire le travail préparatoire n°5)

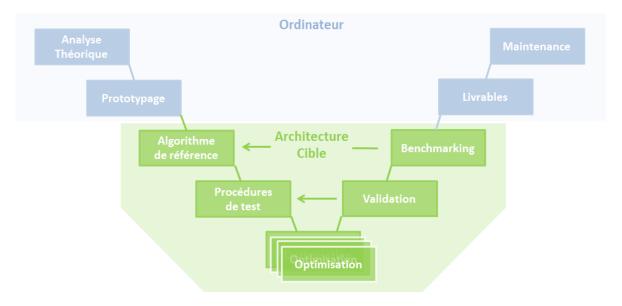

### 1.1. Optimisation algorithmique

Durant cette trame de travaux pratiques, nous allons nous intéresser au workflow typiquement rencontré en milieu industriel dans le cadre d'optimisations logicielles d'algorithmes embarqués sur une cible matérielle spécialisée. Ce processus de développement peut par exemple être rencontré chez les acteurs des grands domaines du traitement du signal (traitement d'antenne, traitement d'image, traitement du son, cloud computing, etc). Nous avons travaillé par le passé et travaillons encore à l'ENSICAEN avec plusieurs partenaires industriels ayant ces types de contraintes (THALES, SAFRAN, CANON, diverses entreprises en traitement d'image, etc).

Nous nous intéresserons à l'implémentation d'un algorithme simple et standard du domaine du traitement du signal, un filtre FIR ou produit scalaire (convolution discrète). Nous nous attarderons sur les stratégies d'optimisation pour une architecture matérielle spécialisée et non à la théorie mathématique associée. Tous nos développements seront guidés par le test, étape pouvant tenir une place très importante dans le temps de développement global d'une application et le Benchmarking (analyse comparative). Observons le workflow de la trame de travaux pratiques :

- Analyse mathématique théorique de l'algorithme sur ordinateur. Optimisation mathématique à cette étape afin de diminuer la complexité algorithmique (notation "grand O" ou "Omicron" de Landau) notamment en MAC (Multiply-Accumulate) pour un algorithme du TNS (Traitement Numérique du Signal)

- Modélisation, conception et validation durant les phases de prototypage sur ordinateur. L'outil logiciel de prototypage rapide le plus rencontré en milieu industriel à notre époque dans le domaine du traitement du signal est Matlab/Simulink (Scilab en version libre). Cette étape est essentielle afin de valider la structure en pseudo code des algorithmes, les procédures de test ainsi que les vecteurs d'entrée et de sortie

- Développement et validation sur cible des procédures de test. Dans le cadre de nos développements, nous nous intéresserons aux tests de conformité/validité (cohérence des valeurs de sortie par rapport à l'algorithme de référence) et de performance (mesures temporelles)

- Développement sur cible d'un algorithme de référence en C canonique ou C naturel

- Développements, tests et validations successives sur cible des stratégies d'optimisation sur architecture processeur spécialisée (vectorisation monocœur, parallélisation multicœur, gestion optimale de la hiérarchie mémoire L1/L2/L3, périphériques d'accélération, périphériques DMA, etc)

### 1.2. Convolution discrète ou filtre FIR

Cette trame de TP consiste à implémenter un algorithme optimisé de filtrage FIR (ou produit scalaire ou convolution discrète) sur une architecture DSP spécialisée pour du calcul numérique. Effectuons quelques rappels sur cet algorithme. Une implémentation courante de ce filtre consiste à appeler périodiquement (période d'échantillonnage) l'algorithme dans une optique de calcul en **temps réel**. A chaque appel, seul un échantillon de sortie est calculé puis traité :

$$y(k) = \sum_{j=0}^{N} a(j).x(k-j)$$

x() = vecteur d'échantillons d'entrée (taille égale à N)

a() = vecteur de coefficients

y(k) = échantillon courant de sortie

k = indice courant

N = ordre du filtre

N+1 = nombre de coefficients

L'implémentation vue en travaux pratiques se fera en **temps différé**. Nous calculerons un vecteur de sortie complet en traitant l'information depuis un vecteur d'entrée pouvant être très long (plusieurs Mo) et dans tous les cas de figure de taille supérieure ou égale au nombre de coefficients (ordre du filtre FIR + 1) :

$$y(k) = \sum_{k=0}^{Y} \sum_{j=0}^{N} a(j).x(k-j)$$

x() = vecteur d'échantillons d'entrée (taille supérieure ou égale à N)

a() = vecteur de coefficients

y() = vecteur d'échantillons de sortie

k = indice courant

N = ordre du filtre

N+1 = nombre de coefficients

Y = taille du vecteur de sortie

Y+N-1 = taille du vecteur d'entrée

La phase de prototypage rapide sous environnement Matlab/Simulink ne sera pas à faire et vous est donnée dans le répertoire de projet /disco/matlab/. Elle est entièrement recouverte par le programme de 1<sup>ière</sup> année en Traitement Numérique du Signal. Nous nous attarderons uniquement sur les problématiques liées à l'intégration et l'optimisation sur DSP VLIW TMS320C6678. Observons l'implémentation en pseudo code Matlab au format flottant simple précision IEEE754 de l'algorithme de filtrage en temps différé précédemment présenté. Comprendre cet algorithme ...

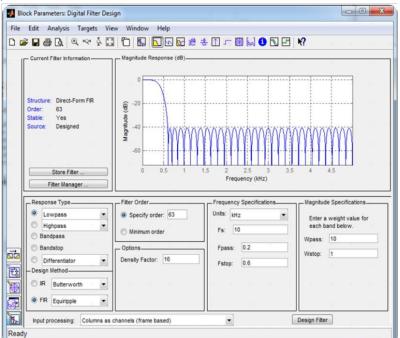

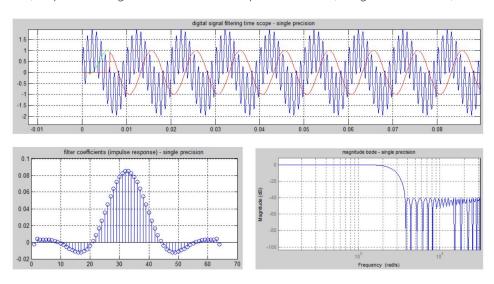

Le filtre à intégrer sur cible ainsi que les vecteurs de test d'entrée ont été générés et validés durant les phases de prototypage sous Matlab/Simulink en utilisant l'outil FDATool (cf. capture ci-dessous):

Le filtre FIR à intégrer est un filtre Passe Bas coupant à 200Hz pour une fréquence d'échantillonnage à 10KHz. Il s'agit d'un filtre ordre 63 comprenant donc 64 coefficients de symétrie paire en flottant simple précision IEEE-754 (cf. ci-dessous). Ce filtre offre un gain unitaire dans la bande passante et une atténuation de -40dB dans la bande coupée. La bande d'atténuation est comprise entre 200Hz et 600Hz. Ce filtre ne vise aucune application ou domaine spécifique et ne nous servira qu'à illustrer les concepts et stratégies d'optimisation sur processeur spécialisé. Le vecteur de test d'entrée est une simple somme de deux sinusoïdes à 100Hz et 1KHz (bleu ci-dessous). Après filtrage, seule l'harmonique à 100Hz (rouge ci-dessous) est identifiable :

### 1.3. Exemple des applications Radar

Radar de défense aérienne GM 400 - THALES AIR SYSTEMS

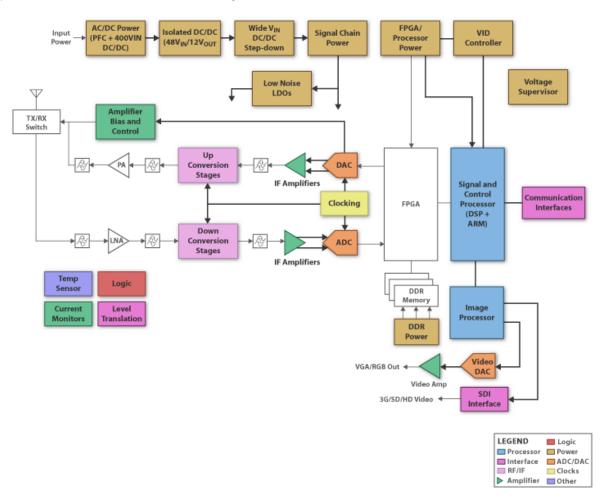

Afin de bien prendre conscience de l'intérêt de tel développement et phases d'optimisation, prenons l'exemple d'une application radar. Nous pouvons observer, ci-dessous, l'architecture matérielle typique d'un radar. Observons l'emplacement du processeur de traitement numérique du signal, dans le cas présent un DSP. Il faut savoir que d'autres familles de processeurs orientés calcul peuvent également remplir cette tâche (FPGA, MPPA, GPP voire GPU), chaque famille offrant son lot d'avantages et d'inconvénients.

Une chaîne numérique de traitement radar implémente également un produit scalaire comme celui étudié dans cette trame de travaux pratiques . A titre indicatif, sans optimisation l'algorithme du produit scalaire représente environ près de 40% du temps de traitement d'une chaîne Radar complète. Compte-tenu des contraintes temps réel excessivement lourdes imposées par ce type d'application, soit quelques Mo de données à traiter en quelques ms, nous pouvons pressentir tout l'intérêt de développer des bibliothèques de fonctions de calcul spécialisées pour l'architecture cible. Ce sera l'objectif premier de cet enseignement tout en respectant des méthodologies assurant un développement optimal.

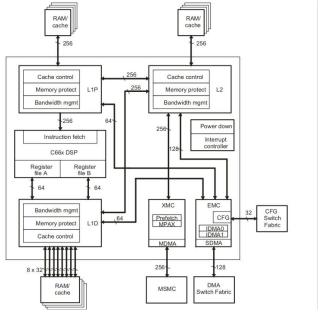

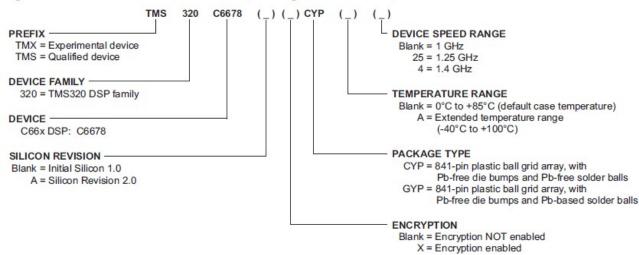

### 1.4. Architecture DSP VLIW C6600 de TI

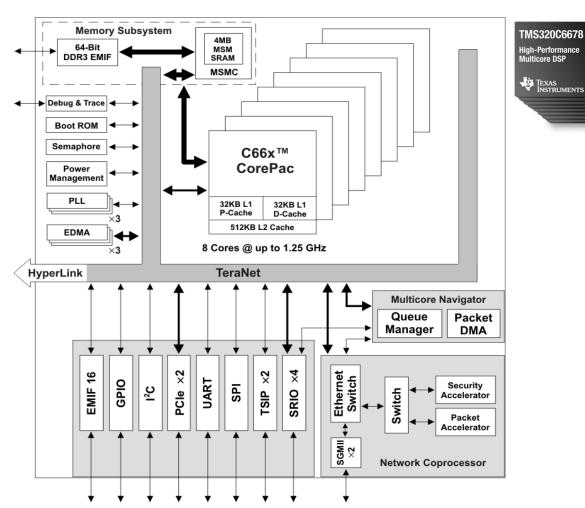

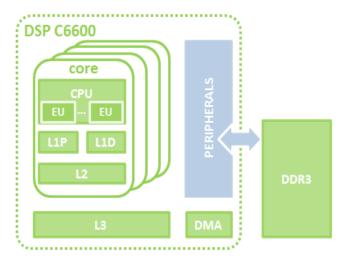

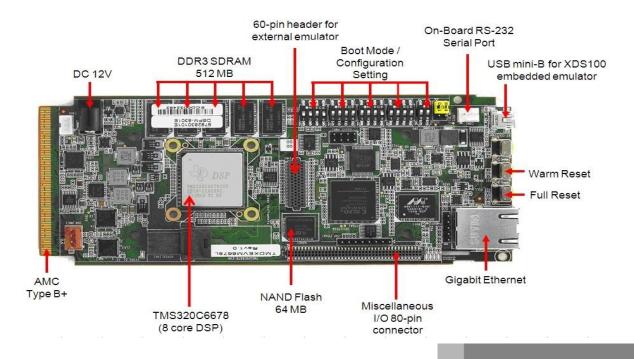

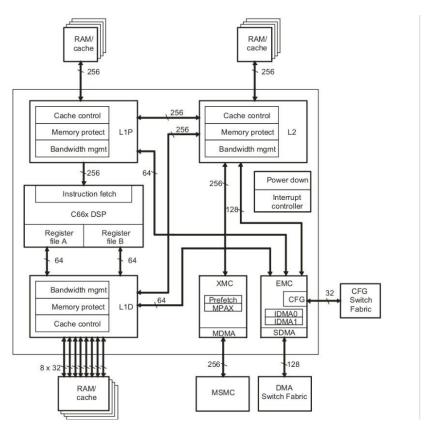

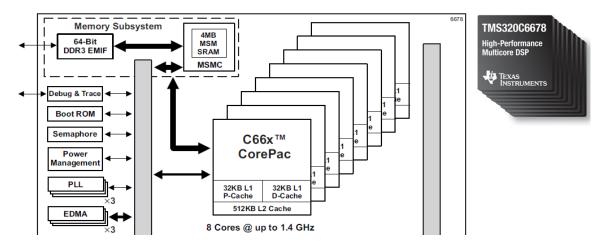

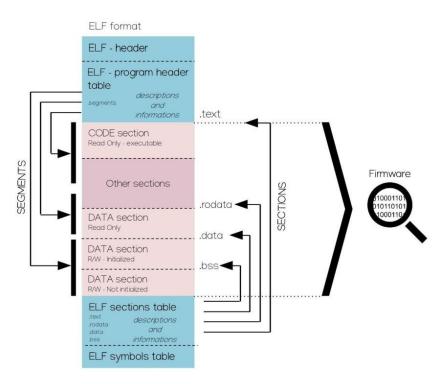

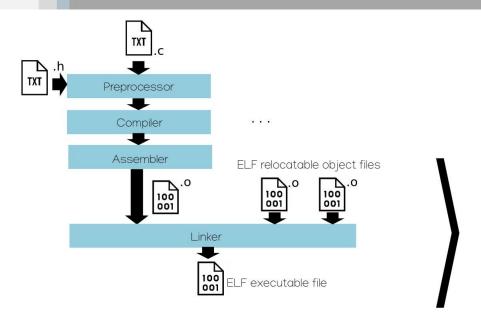

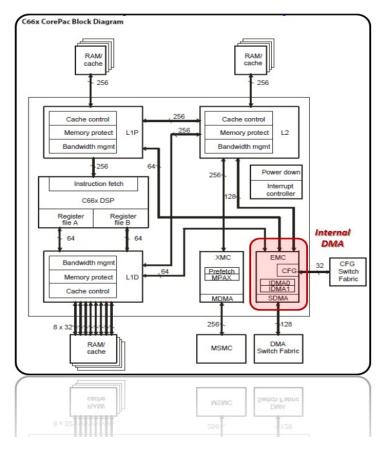

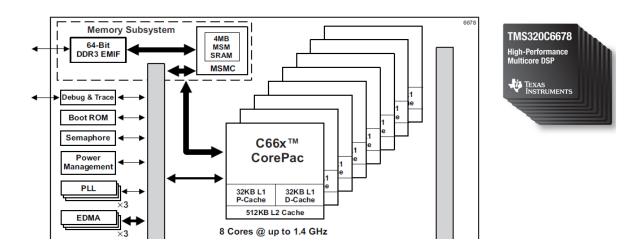

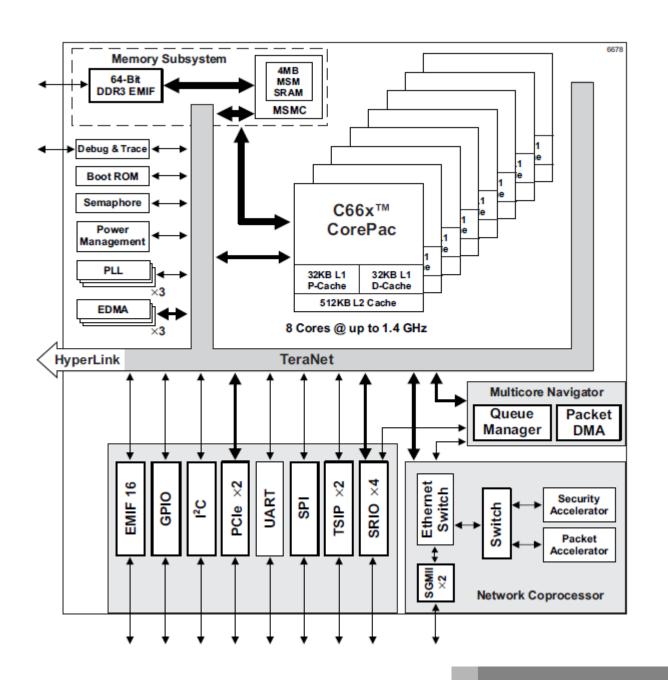

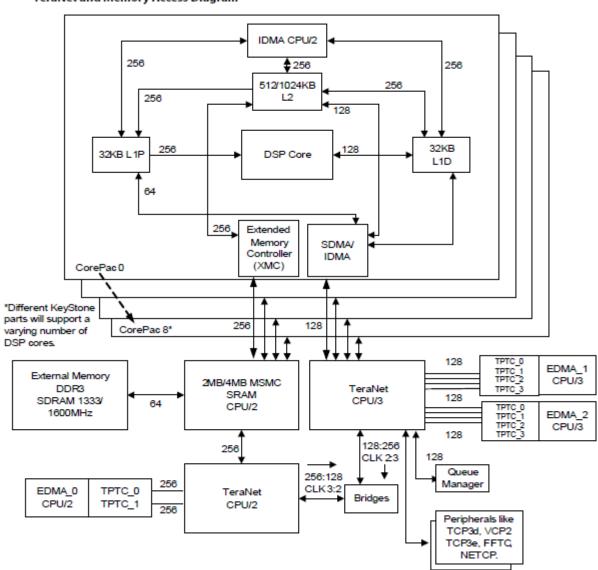

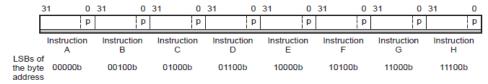

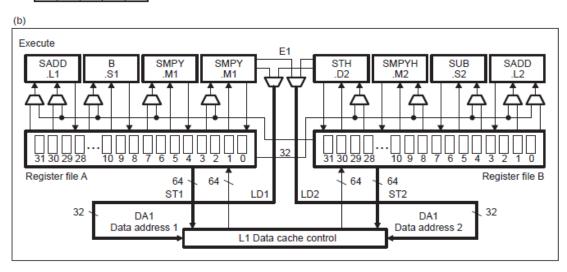

Nos développements seront réalisés sur l'architecture DSP VLIW C6600 (Very Long Instruction Word) proposée par TI ou Texas Instruments (processeur utilisé par certains partenaires). Pour information, à notre époque la famille CPU C6000 de TI est l'architecture CPU leader sur le marché des processeurs DSP (Digital Signal Processor). Le processeur C6678 étudié en TP étant l'un des composants haut de gamme de la famille avec ses 8 cœurs vectoriels VLIW. Cette architecture propose quelques atouts assurant une grande flexibilité et permettant une bonne compréhension des architectures processeurs actuelles. Le processeur DSP TMS320C6678 offre les services matériels illustrés ci-dessous :

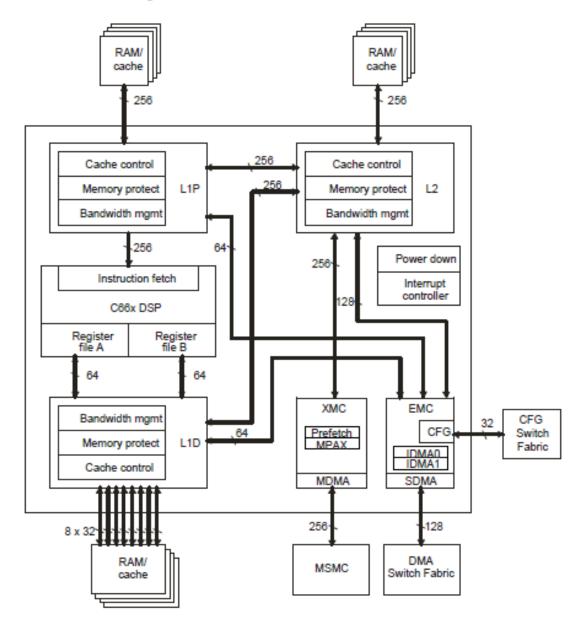

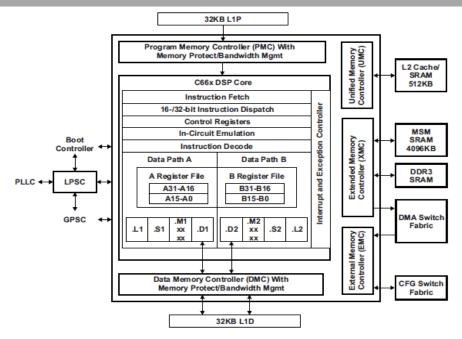

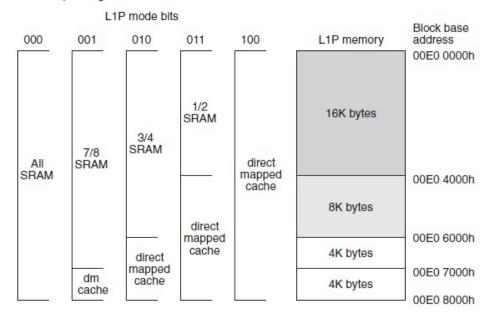

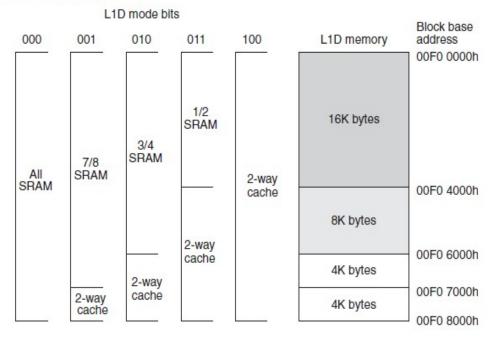

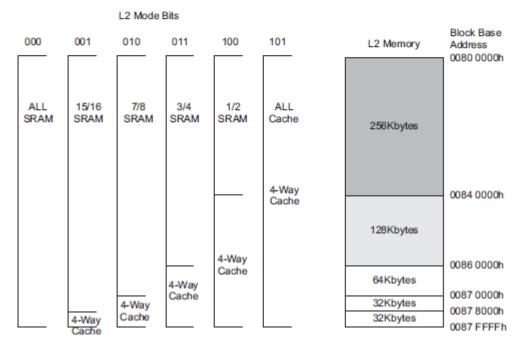

- 8 cœurs avec CPU vectoriels VLIW possédant chacun 32Ko caches L1P (L1-Program) et L1D (L1-Data), ainsi que 512Ko de cache L2 unifié (Program/Data)

- Chaque cœur peut être cadencé jusqu'à 1,4GHz

- Le niveau mémoire L3 unifié de 4Mo nommé MSM (Multi-core Shared Memory) est partagé entre cœurs

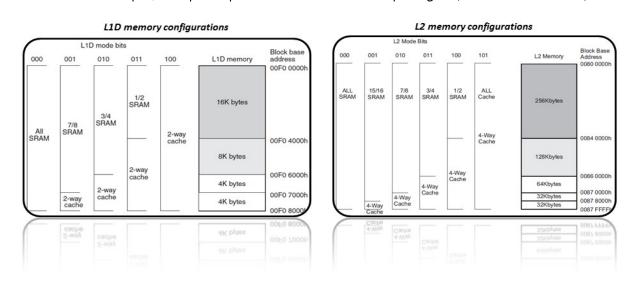

- Chaque niveau mémoire peut être configurable en cache ou en mémoire adressable **SRAM** permettant une architecture matérielle configurable en modèle mémoire uniforme UMA ou non-uniforme NUMA. Chose impossible sur processeur généraliste GPP Inte/AMD x86 64 par exemple.

- De la mémoire SDRAM DDR3 externe peut également être ajoutée sur circuit imprimé et est alors interconnectée via le périphérique d'interface EMIF (External Memory Interface).

TEXAS INSTRUMENTS

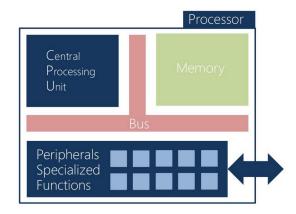

En première année, nous avons découvert les bases du développement sur processeur numérique MCU (Micro Controller Unit) ou microcontrôleur. Ces processeurs étant généralistes et non spécialisés pour du calcul numérique, nous nous sommes donc assez longuement attardés sur les périphériques de communication (UART, I2C, etc) et d'interface (GPIO, ADC, etc) :

Cet enseignement est différent et doit être perçu comme une extension des compétences de première année. Cette année nous allons travailler sur machine fortement parallèle et nous nous efforcerons de comprendre puis d'exploiter au mieux les ressources matérielles proposées par notre processeur. Les périphériques d'interface ne seront donc pas vus, seule la partie traitement nous intéressera. Nous nous focaliserons sur :

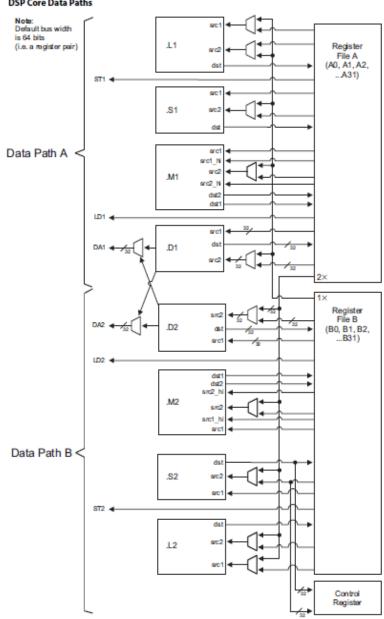

- CPU vectoriel VLIW (pipelining software d'instructions et vectorisation des données)

- Mémoires L1/L2/L3 configurables en SRAM adressable ou en Cache et mémoire DDR

- Périphériques DMA (Direct Memory Access) de copie mémoire (copies sans passer par le CPU)

Même si l'exemple qui suit n'a que peu de sens, afin de bien comprendre les différences majeures entre les architectures de première année et de cette année, comparons les performances théoriques maximales des deux processeurs. Avec ces quelques chiffres, nous pouvons commencer à pressentir le potentiel pour du calcul numérique flottant de cette famille de processeur.

- Un MCU 8bits entier PIC18F27K40 de Microchip peut exécuter jusqu'à 16MIPS (soit 16 millions instructions entières 8bits par seconde)

- Un DSP VLIW 32bits flottant TMS320C6678 de Texas Instruments peut exécuter jusqu'à 22,4GFLOP/core (soit 22,4 Giga instructions flottantes 32bits en simple précision IEEE-754 par seconde et par cœur). Soit jusqu'à 179,2GFLOP pour le processeur complet grâce à ses 8 cœurs, le tout avec une horloge à 1,4GHz.

### 1.5. Objectifs pédagogiques

Nous venons de présenter un rapide tour d'horizon du potentiel de notre architecture processeur. Nous comprenons mieux le sens du nom de l'enseignement "Architectures pour le calcul". Beaucoup des **mécanismes d'accélération déterministes** (temps réel) présentés sont impossibles ou en tous cas moins performants ou moins déterministes sur architectures généralistes (GPP ou AP avec MMU/Cache). Néanmoins, une bonne compréhension des stratégies présentées précédemment vous assurera une adaptabilité forte pour des problématiques d'optimisation sur la plupart des architectures processeurs parallèles du marché (GPP, DSP, MPPA, GPU et MCU vectoriel). En milieu industriel, les ingénieurs bas niveau chargés du développement des bibliothèques spécialisées et système possèdent des compétences différentes des ingénieurs haut niveau assurant l'intégration logicielle et le développement des applications :

- Développeur système temps réel bas niveau (système, driver ou algorithmique) : ingénieur spécialisé dans les architectures matérielles processeurs et le développement de bibliothèques spécialisées. Maîtrise forte de l'architecture, des outils de développement, des langages C/ASM et du fonctionnement de la machine.

- Développeur logiciel applicatif haut niveau : concepteur et intégrateur applicatif haut niveau travaillant dans les couches hautes de l'application et utilisant les API et bibliothèques en mode boîtes noires (faible voire aucune idée de l'implémentation réelle bas niveau). Maîtrise faible de l'architecture et du fonctionnement de la machine.

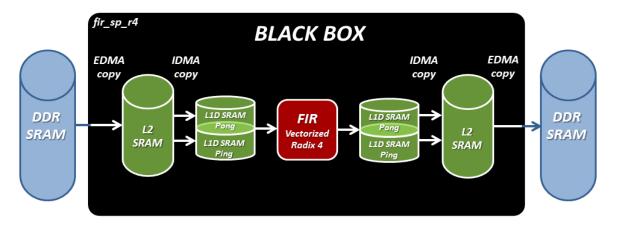

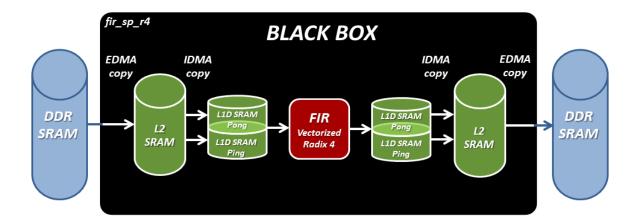

Cette trame d'enseignement vise donc à ouvrir les portes des stages et des métiers dédiés à l'optimisation et l'accélération algorithmique sur processeur spécialisé. Ces compétences, rares sur le marché, sont demandées par des entreprises ayant ce type de besoin spécifique (THALES, SAFRAN, ARIANE GROUP, sociétés en traitement d'image, cloud computing, etc). Par exemple, un élève ingénieur réalisant la trame complète, aura développé en fin d'enseignement un seul et unique algorithme fir\_sp\_r4 (~30-40h de développement équivalent à une voire deux semaines entreprise). Cependant cet algorithme implémente certaines subtilités d'intégration :

- Copies montantes et descendantes des données entre DDR et L2 SRAM réalisées par DMA

- Copies montantes et descendantes des données entre L2 SRAM et L1D SRAM avec alternance des buffers de stockage (ping-pong) par IDMA interne à chaque Cœur

- Vectorisation C intrinsèque avec déroulement de boucle en base 4 sur CPU DSP VLIW

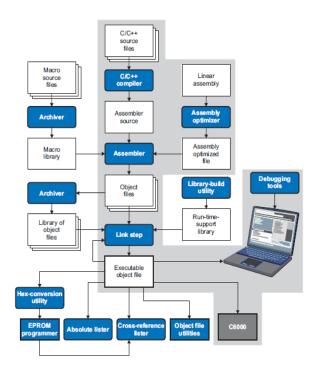

### 1.6. Outils de développement

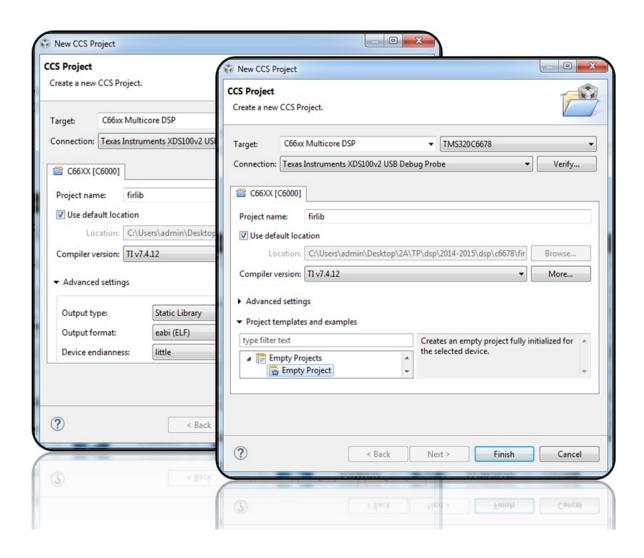

Nous développerons sous **IDE CCS5.5** (Code Composer Studio) développé par Texas Instruments et basé sur un framework libre Eclipse. Les outils de développement et bibliothèques sont librement téléchargeables et installables depuis internet. Se référer à la page moodle de l'enseignement pour l'installation des outils de développement (section – OUTILS DE DEVELOPPEMENT):

### https://foad.ensicaen.fr/course/view.php?id=117

La trame de travaux pratiques sera réalisée sur la plateforme de développement TMDXEVM6678L EVM (Evaluation Module) proposée par la société Advantec. Cette maquette d'évaluation embarque notamment une sonde de programmation USB XDS100 assurant la programmation et le débogage des applicatifs. Pour information, les outils de développement logiciel deviennent payants si nous souhaitons travailler avec des sondes d'émulation évoluées, telle que la sonde XDS560 également présente à l'école pour des phases de projet industriel. :

### https://www.ti.com/tool/TMDSEVM6678

## 1.7. Benchmarking

| ANALYSE COMPARATIVE                                |                             |                                     |                            |                                     |                                                                                                                                                      |  |  |  |  |  |  |

|----------------------------------------------------|-----------------------------|-------------------------------------|----------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Algorithme<br>vecteur d'entré 2K<br>samples ou 8Ko | Architecture                | Temps<br>d'exécution<br>ms / Cycles | Performances < 8 MACS max. | Temps de<br>Développement<br>heures | Observations et Limitations                                                                                                                          |  |  |  |  |  |  |

| DSPF_sp_fir_gen                                    |                             | 0.031ms<br>43695cy                  | 3.0                        | 0                                   | cf. documentation DSPLIB TI nr and nh are a multiples of 4 and greaters than or equals to 4. x, h and r are double-word aligned. Interruptible code. |  |  |  |  |  |  |

|                                                    |                             |                                     |                            |                                     |                                                                                                                                                      |  |  |  |  |  |  |

|                                                    |                             |                                     |                            |                                     |                                                                                                                                                      |  |  |  |  |  |  |

|                                                    | Texas<br>Instr.<br>DSP VLIW |                                     |                            |                                     |                                                                                                                                                      |  |  |  |  |  |  |

|                                                    | C6600                       |                                     |                            |                                     |                                                                                                                                                      |  |  |  |  |  |  |

|                                                    |                             |                                     |                            |                                     |                                                                                                                                                      |  |  |  |  |  |  |

|                                                    |                             |                                     |                            |                                     |                                                                                                                                                      |  |  |  |  |  |  |

|                                                    | Intel<br>GPP<br>superscalar |                                     |                            |                                     |                                                                                                                                                      |  |  |  |  |  |  |

|                                                    | corei7<br>Haswell<br>IA-64  |                                     |                            |                                     |                                                                                                                                                      |  |  |  |  |  |  |

©creative (©©)

# TRAVAUX PRATIQUES

PROGRAMMATION VECTORIELLE SUR DSP VLIW C6600

# ARCHITECTURES POUR LE CALCUL

### SOMMAIRE

### 2. PROGRAMMATION VECTORIELLE SUR DSP VLIW C6600

- 2.1. Création du projet de test2.2. Analyse du programme de test

- 2.3. Assembleur canonique C6600

- 2.4. Assembleur VLIW C6600

- 2.5. Pipelining software en assembleur C6600

- 2.6. Vectorisation en assembleur C6600

- 2.7. Déroulement de boucle en C canonique

- 2.8. Vectorisation en C intrinsèque

### 2.1. Création du projet de test

Parcourir puis s'aider des ressources en annexes durant les travaux pratiques (création de projet CCS, extraits de datasheet TMS320C6678, jeu d'instructions, etc). Toutes les documentations techniques utiles se trouvent dans le répertoire **tp/doc/datasheet**. Pour information, Texas instruments propose un cours en ligne gratuit sur sa famille CPU C6000 :

### https://training.ti.com/c6000-embedded-design-workshop

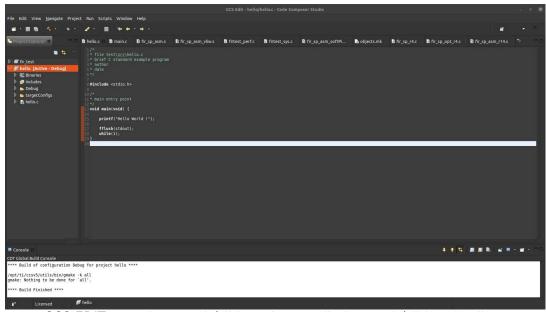

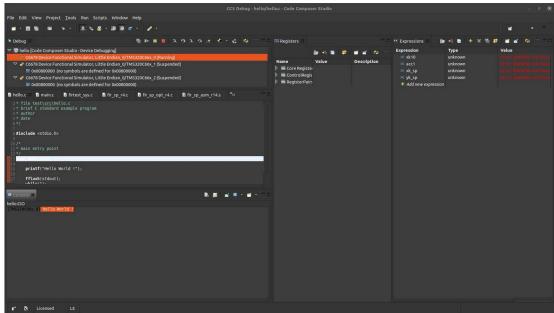

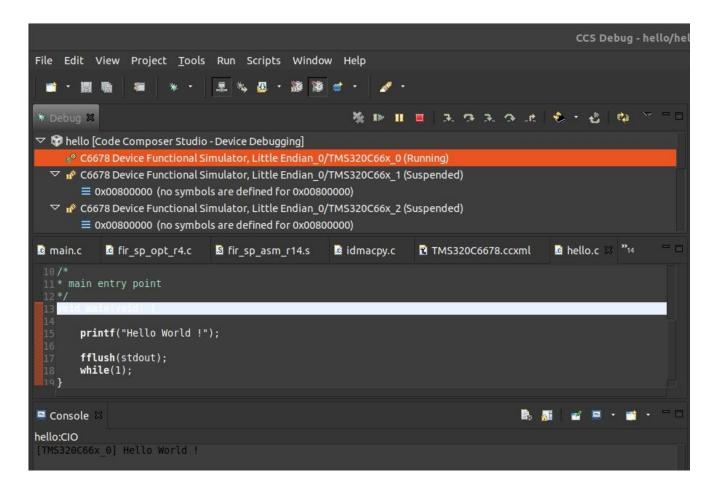

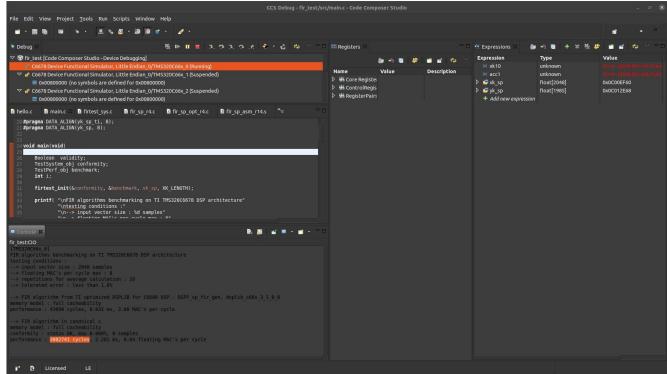

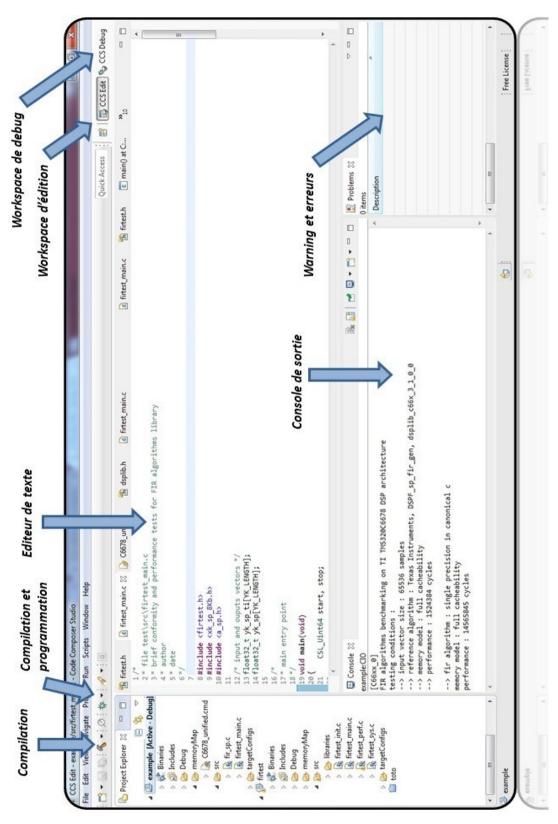

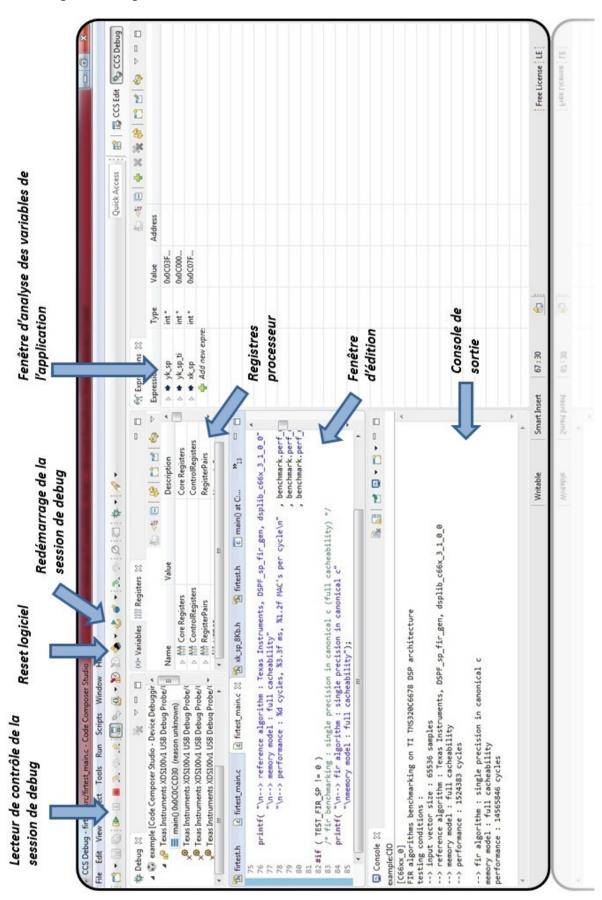

• Créer un projet CCS nommé hello dans le répertoire /disco/c6678/hello/ incluant le fichier source /disco/c6678/hello/hello.c (cf. image CCS EDIT ci-dessous). S'assurer de la bonne compilation et exécution du projet (5-10mn). Observer la sortie dans la fenêtre de Console (cf. image CCS DEBUG ci-dessous). Ce projet ne réalise qu'un printf et n'a pour objectif que de valider ''rapidement'' le bon fonctionnement de l'IDE CCS 5.5 (maintenant d'une génération et version ancienne). Lire les 3 pages suivantes pour vous aiguiller. Une fois fonctionnel et validé sur simulateur voire sur cible, ce projet peut être fermé et ne sera plus utilisé durant la totalité de la trame!

CCS EDIT - Workspace d'édition, de compilation et d'édition des liens

CCS DEBUG - Workspace de test, de debug et de validation

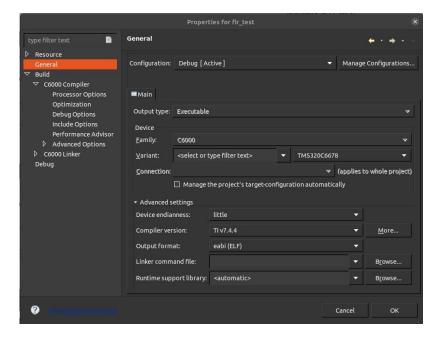

• File > New > CCS Project pour créer le projet CCS :

• Project Name : hello

Output : Executable

Location : <your path>/disco/c6678/hello

• Family : C6000

Variant : C66xx Multicore DSP > TMS320C6678

Connection: Texas Instruments XDS100 v2 USB Emulator

Project templates and examples : Empy Projects > Empty Project

#### Finish

- [Clic droit] sur le nom du projet dans Project Explorer pour ajouter un fichier :

- Add Files...

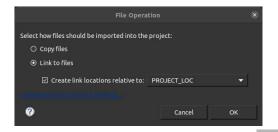

- Ajouter hello.c et spécifier Link to File

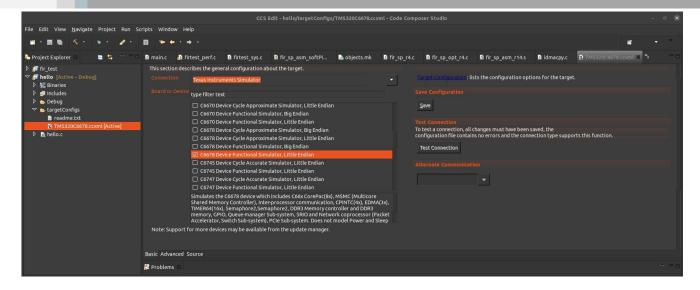

- Project Explorer > hello > targetConfigs > TMS320C6678.ccxml pour configurer le mode simulateur de CCS :

- Connection: Texas Instruments Simulator

- Board or Device : C6678 Device Functional Simulator, Little Endian

- Save

- icône Marteau pour compiler le projet (workspace CCS EDIT) :

- icône scarabée pour charger et tester l'exécutable dans le simulateur (workspace CCS DEBUG)

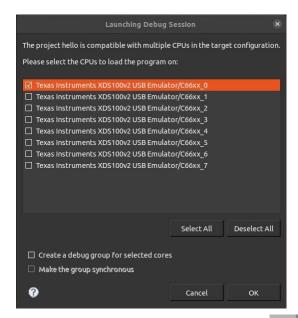

- Charger le programme sur le cœur n°0 seulement (et non sur les 8 cœurs du DSP):

- Deselect All

- [x] ..../C66xx 0 pour sélectionner le cœur n°0

- OK

Tester le projet (icône flèche verte / play – workspace de debug)

• Observer la sortie (fenêtre Console – workspace de debug)

### [TMS320C66x 0] Hello World Bro's!

- Arrêter la session de debug (icône carré rouge / stop workspace de debug)

- Passer à la suite!

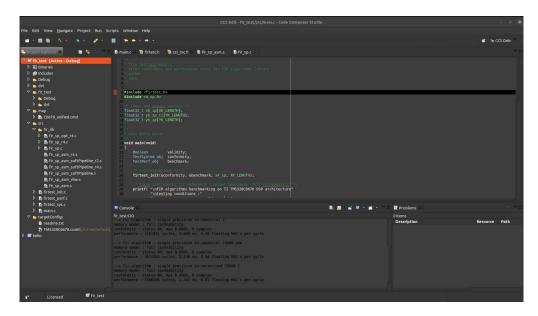

- Créer le projet de test nommé fir\_test dans le répertoire /disco/c6678/test/pjct/. S'assurer de la bonne compilation (cf. image CCS EDIT ci-dessous) et exécution du projet. Observer la sortie dans la fenêtre de Console (cf. image CCS DEBUG ci-dessous). Inclure les fichiers sources suivants et s'aider des 3 pages suivantes comme des 3 précédentes :

- ~/disco/c6678/test/src/\*.c (à ajouter sous CCS dans src)

- ~/disco/c6678/firlib/src/\*.c (à ajouter sous CCS dans un répertoire logique src/lib)

- ~/disco/c6678/firlib/src/\*.s (à ajouter sous CCS dans un répertoire logique src/lib)

- ~/disco/c6678/test/map/C6678 unified.cmd (à ajouter sous CCS dans memorymap)

```

CCS Edit - Pr_test/prr/maint. - Code Composer Studio

| CCS Edit - Pr_test/prr/maint. - Code Composer Studio

| CCS Edit - Pr_test/prr/maint. - Code Composer Studio

| CCS Edit - Pr_test/prr/maint. - Code Composer Studio

| CCS Edit - Pr_test/prr/maint. - Code Composer Studio

| CCS Edit - Pr_test/prr/maint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - Code Composer Studio

| CCS Edit - Pr_test/primaint. - CCS Edit - Pr_test/pr_test. - CCS Edit - Pr_te

```

CCS EDIT - Workspace d'édition, de compilation et d'édition des liens

CCS DEBUG - Workspace de test, de debug et de validation

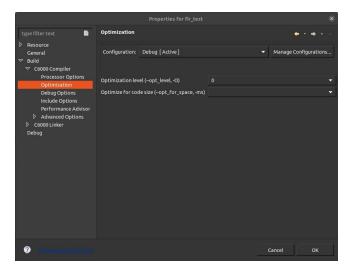

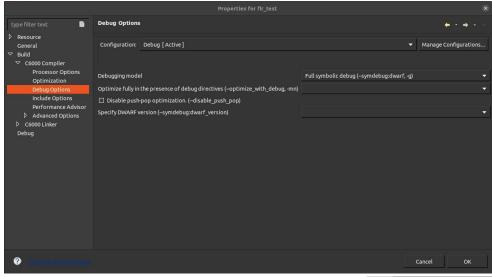

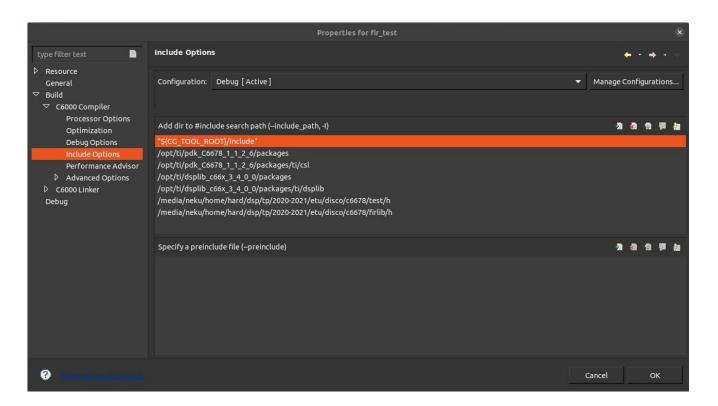

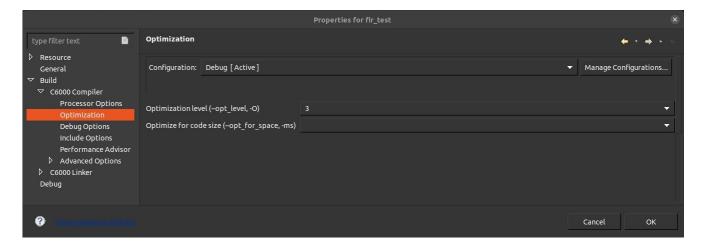

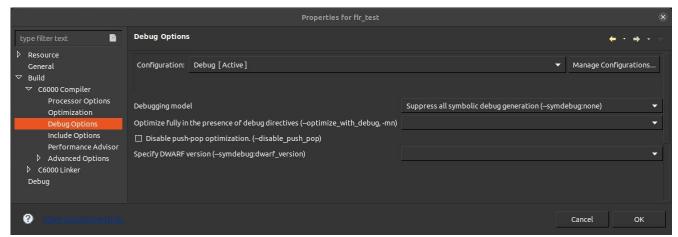

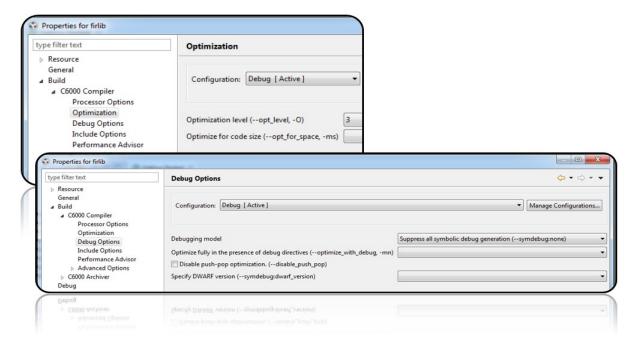

- Project Explorer > votre\_projet\_fir\_test [Active Debug] > clic droit > Properties

- Vérifier la configuration générale du projet

· Vérifier la configuration du projet en mode debug

- Vérifier l'inclusion des chemins pour permettre au compilateur de trouver les fichiers d'entête nécessaires au projet (C6000 compiler) :

- Attention, fichiers d'en-tête et bibliothèques CSL (Chip Support Library) et DSPLIB (DSP Library) de TI installées dans /opt/ti sous GNU\Linux

- Attention, fichiers d'en-tête et bibliothèques CSL (Chip Support Library) et DSPLIB (DSP Library) de TI installées dans C:\ti sous Windows

- Fichiers d'en-tête applicatifs pour le projet de test

<your project path>/disco/c6678/test/h

• Fichiers d'en-tête applicatifs pour la bibliothèque projet FIRLIB

<your\_project\_path>/disco/c6678/firlib/h

• Fichiers d'en-tête de la bibliothèque CSL (Chip Support Library) de TI

<depends\_on\_your\_system>/ti/pdk\_C6678\_1\_1\_2\_6/packages

• Fichiers d'en-tête de la bibliothèque CSL (Chip Support Library) de TI

<depends\_on\_your\_system>/ti/pdk\_C6678\_1\_1\_2\_6/packages/ti/csl

• Fichiers d'en-tête de la bibliothèque DSPLIB (Digital Signal Processing Library) de TI

<depends\_on\_your\_system>/ti/dsplib\_c66x\_3\_4\_0\_0/packages

• Fichiers d'en-tête de la bibliothèque DSPLIB (Digital Signal Processing Library) de TI

<depends on your system>/ti/dsplib c66x 3 4 0 0/packages/ti/dsplib

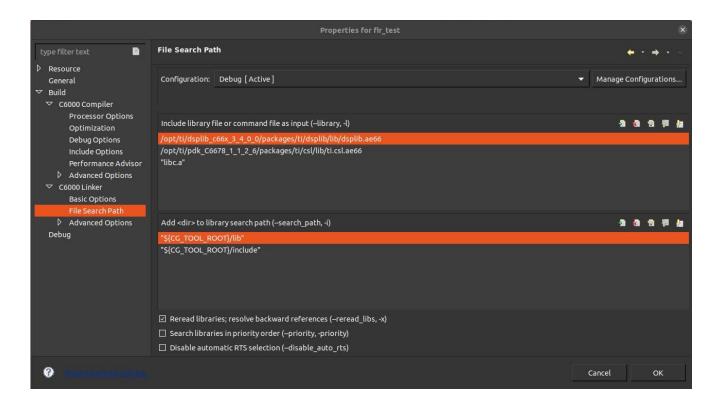

- Vérifier l'ajout des bibliothèques nécessaires au projet pour l'édition de liens (C6000 linker):

- Attention, fichiers d'en-tête et bibliothèques CSL (Chip Support Library) et DSPLIB (DSP Library) de TI installées dans /opt/ti sous GNU\Linux

- Attention, fichiers d'en-tête et bibliothèques CSL (Chip Support Library) et DSPLIB (DSP Library) de TI installées dans C:\ti sous Windows

- Bibliothèque CSL (Chip Support Library) pour DSP TMS320C6678

- <depends\_on\_your\_system>/ti/pdk\_C6678\_1\_1\_2\_6/packages/ti/csl/lib/ti.csl.ae66

- Bibliothèque DSPLIB (Digital Signal Processing Library) pour DSP TMS320 famille C6600

<depends\_on\_your\_system>/ti/dsplib\_c66x\_3\_4\_0\_0/packages/ti/dsplib/lib/dsplib.ae66

- Cliquer sur OK pour quitter les propriétés du projet

- Compiler votre projet (icône scarabée workspace d'édition)

- Tester le projet (icône flèche verte / play workspace de debug)

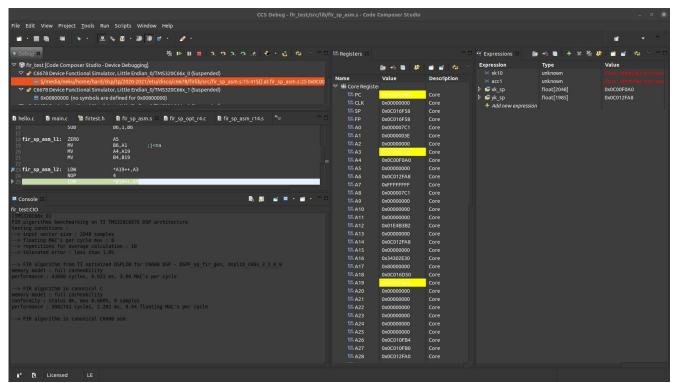

- Observer la sortie (fenêtre Console workspace de debug) ainsi que les mesures de performances :

- Algorithme de référence TI présent dans la DSPLIB : ~43690 cy (soit ~0.031ms)

- Algorithme de filtrage FIR en C canonique : ~3082742 cy (soit ~2.202ms)

- Arrêter la session de debug (icône carré rouge / stop workspace de debug)

- Passer à la suite!

### 2.2. Analyse du programme de test

- Analyser le projet de test complet (10-15mn) puis répondre aux questions suivantes. Fichiers main.c, firtest.h, firtest init.c, firtest sys.c et firtest perf.c?

- Dans le fichier firtest.h, quel est le rôle des macros ci-dessous ?

```

#define TEST_FIR_SP 1

#define TEST_FIR_SP_R4 0

#define TEST_FIR_SP_OPT_R4 0

#define TEST_FIR_ASM 0

#define TEST_FIR_ASM_VLIW 0

#define TEST_FIR_ASM_PIPE 0

#define TEST_FIR_ASM_R4 0

```

• Dans le fichier firtest\_init.c, que réalise la ligne ci-dessous ?

```

CSL_tscEnable();

```

Dans le fichier firtest\_perf.c, que réalisent les lignes ci-dessous ?

```

start = CSL_tscRead ();

...

end = CSL_tscRead ();

```

• Dans le fichier main.c (test de la fonction fir\_sp), à quoi correspond le champ &fir\_sp passé comme argument à la fonction firtest perf ?

```

firtest_perf (&benchmark, UMA_L2CACHE_L1DCACHE, yk_sp, &fir_sp);

```

• Dans le fichier firtest perf.c, que réalise la ligne ci-dessous ?

```

(*fir_fct) (xk_sp, a_sp, output, A_LENGTH, YK_LENGTH);

```

• Dans le fichier **main.c**, quels champs contiennent les variables structurées suivantes ? Quel est le rôle de chaque champ ?

```

TestSystem_obj conformity;

TestPerf_obj benchmark;

```

• En vous aidant du fichier **firtest\_sys.c** voire d'autres fichiers, quelle est la marge d'erreur tolérée par la procédure de test de la conformité/validité de l'algorithme par défaut ?

### 2.3. Assembleur canonique C6600

Dans le fichier firtest.h, mettre la macro TEST\_FIR\_ASM à 1

#define TEST FIR ASM

• En vous aidant du cours, implémenter le code de la fonction fir\_sp\_asm puis valider son fonctionnement. Cette fonction implémente l'algorithme de filtrage FIR en assembleur canonique C6600 sans optimisation. Ne pas oublier les delay slot (NOP) dans votre implémentation.

CCS DEBUG - Workspace de test, de debug et de validation

- Conseils pour Debugger le programme :

- Travailler en mode Debug

- Compiler et se placer dans l'espace de travail CCS Debug (Workspace de test, de debug et de validation)

- Ouvrir la fenêtre Registers > Core Registers (cf. ci-dessus) afin d'observer le contenu des registres CPU (fenêtre accessible par Window > Show View). La fenêtre Expressions vous permet de voir le contenu des tableaux sous tests.

- Placer des points d'arrêts dans votre programme sous test en réalisant un double clic dans la fenêtre d'édition sur le numéro d'une ligne (cf.ci-dessus – point bleu). La flèche représente l'adresse actuelle pointée par le PC (Program Counter – future instruction à exécuter) dans l'étage de FETCH du CPU (cf. cidessus).

- Exécuter pas à pas le programme CCS Debug > Run > Assembly Step ou F5 ou en utilisant le bandeau de contrôle du programme (cf. ci-dessous)

- Conseils d'implémentation :

- Étape n°1 : s'assurer que l'appel et le retour de la procédure se déroulent bien puis vérifier les valeurs des paramètres d'entrée de la fonction.

- Étape n°2 : implémenter la boucle vide avec la condition de sortie associée.

S'assurer du bon nombre d'itérations et du fait de quitter celle-ci.

- Étape n°3: dans la boucle, vérifier les premiers chargements de données de la mémoire vers le cœur ainsi que la validité des données pré-chargées.

- Étape n°4 : écrire le code correspondant au produit scalaire dans le cœur de la boucle. Cette partie est plus complexe à tester et à valider.

- Remarques : de façon générale, toujours tester les valeurs limites (condition de sortie de boucle, débordement de tableau, valeurs des pointeurs en mémoire ...)

- Après validation en mode Debug, lancer une exécution en mode Release (cf. ci-dessous), compiler, tester puis reporter les résultats des tests dans le tableau d'analyse comparative ou Benchmarking présent dans le document de Prélude.

- Projet Explorer > votre\_projet\_fir\_test [Active Debug] > clic droit > Properties

Une fois la mesure réalisée, se remettre en configuration initiale en mode Debug. Toujours garder le mode Debug pour les phases de développement et le mode Release pour les phases de mesure

### 2.4. Assembleur VI IW C6600

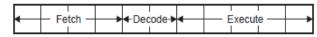

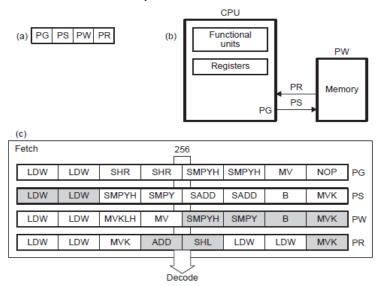

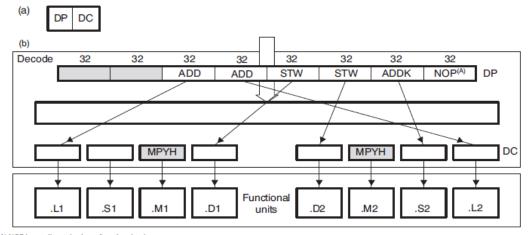

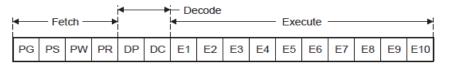

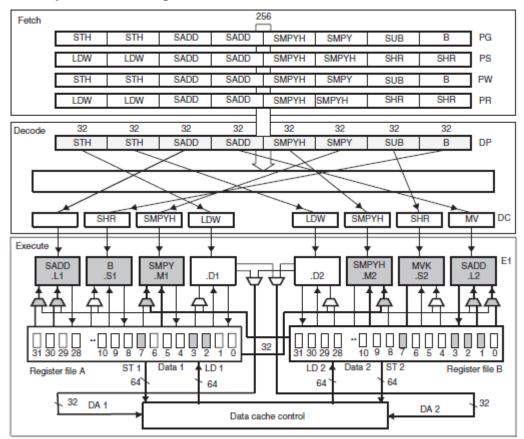

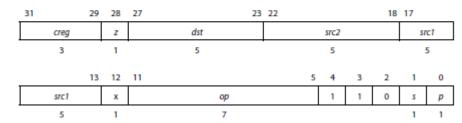

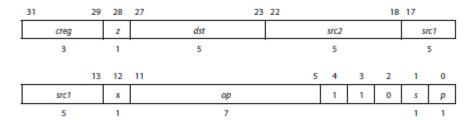

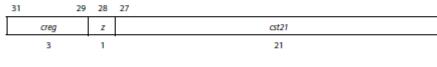

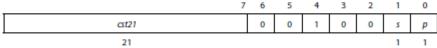

Contrairement aux processeurs superscalaires, les architectures CPU VLIW (Very Long Instruction Word) et EPIC (Explicitly Parallel Instruction Computing) ont pour point commun d'avoir un code Out-Of-Order en mémoire (OOO ou dans le désordre) mais offrant une exécution in-order (exécution et sortie du pipeline dans l'ordre). Dans cet exercice, nous allons jouer sur ce point sans pour autant utiliser d'instructions vectorielles ni tenter d'avoir une utilisation optimale du pipeline logiciel d'instructions du CPU. En effet, nous n'utiliserons que des instructions scalaires (MPYSP, ADDSP, etc).

Rappelons le principe de ce type d'optimisation, uniquement applicable sur architecture CPU VLIW et EPIC (MPPA Kalray, DSP TI C6000, NXP TriMedia, DSP SHARC Analog Device, ST200 STMicroelectronics, Intel Itanium, etc). L'exemple qui suit présente un avancement de branche d'exécution sur architecture C6600. Le code est alors dans le désordre en mémoire et pourtant les deux files d'instructions ci-dessous réalisent le même traitement seulement l'une sortira le résultat plus rapidement :

| Canonical C6600 assembly instructions in-order in memory (processing time : 14 CPU cycles) | VLIW C6600 assembly instructions out-of-order in memory (processing time : 7 CPU cycles) |  |  |  |  |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|--|

| MPYSP A3, B9, A17 NOP 3 FADDSP A17, A5, A5 NOP 2 [A1] SUB A1, 1, A1 [A1] B L2 NOP 5        | MPYSP A3,B9,A17     [A1] SUB A1,1,A1  [A1] B L2  NOP 2  FADDSP A17,A5,A5  NOP 2          |  |  |  |  |

• Dans le fichier firtest.h, mettre la macro TEST FIR ASM VLIW à 1

### #define TEST\_FIR\_ASM\_VLIW

- En vous aidant du cours, implémenter le code de la fonction fir\_sp\_asm\_vliw puis valider son fonctionnement. Cette fonction implémente l'algorithme de filtrage FIR en assembleur C6600 avec optimisation propre aux architectures VLIW (avancement de branches, exécutions d'instructions en parallèle, remplacement de NOP, etc). Ne pas oublier les delay slot (NOP) dans votre implémentation.

- Après validation en mode Debug, lancer une exécution en mode Release, compiler, tester puis reporter les résultats des tests dans le tableau d'analyse comparative ou Benchmarking présent dans le document de Prélude.

- Une fois la mesure réalisée, se remettre en configuration initiale en mode Debug. Toujours garder le mode Debug pour les phases de développement et le mode Release pour les phases de mesure

### 2.5. Pipelining software en assembleur C6600

Dans cet exercice, nous allons nous efforcer d'obtenir une utilisation optimale du pipeline logiciel d'instruction pour notre algorithme écrit en assembleur canonique. Cet exercice consiste à jouer sur le nombre d'unités d'exécution en essayant d'utiliser le CPU au maximum de son potentiel théorique. Dans notre cas, chaque cœur possédant 8 unités d'exécution (.M1, .M2, .L1, .L2, .S1, .S2, .D1 et .D2), toutes capables de travailler en parallèle. Nous chercherons à obtenir un maximum de 8 instructions exécutées par cycle CPU (notamment pour le code du cœur de l'algorithme). Nous allons donc nous intéresser au parallélisme d'instructions. Nous verrons le parallélisme des données à l'exécution dans les prochains exercices sur la vectorisation.

Pour notre algorithme, sans déroulement de boucle (vectorisation des données), le facteur optimal d'optimisation en terme d'accélération sera obtenu à travers cet exercice. Observons de façon graphique dans un tableau l'architecture du code à implémenter. Dans la table de programmation ci-dessous, vous trouverez une implémentation de la boucle interne, la boucle externe restant inchangée. Le prolog est exécuté une seule fois, la boucle kernel autant de fois qu'il y a d'itérations de boucles en retranchant la profondeur du prolog et l'epilog sera également exécuté qu'une seule fois. L'allocation et le choix des registres utilisés reste libre dans le cadre de cet exercice.

|                            | Unités d'Exécution<br>(occupation des pipelines hardware et software) |       |      |        |     |     |     |     |  |  |  |

|----------------------------|-----------------------------------------------------------------------|-------|------|--------|-----|-----|-----|-----|--|--|--|

|                            | .D1                                                                   | .M1   | .S1  | .L1    | .L2 | .S2 | .M2 | .D2 |  |  |  |

|                            | LDW                                                                   |       |      |        |     |     |     | LDW |  |  |  |

|                            | NOP                                                                   |       |      |        |     |     |     | NOP |  |  |  |

|                            | NOP                                                                   |       |      |        |     |     |     | NOP |  |  |  |

| P<br>R                     | NOP                                                                   |       |      |        |     |     |     | NOP |  |  |  |

| O<br>L                     | NOP                                                                   |       |      |        |     |     |     | NOP |  |  |  |

| 0                          | LDW                                                                   | MPYSP |      |        |     |     |     | LDW |  |  |  |

| G                          | NOP                                                                   | NOP   |      |        |     |     |     | NOP |  |  |  |

|                            | NOP                                                                   | NOP   |      |        |     |     |     | NOP |  |  |  |

|                            | NOP                                                                   | NOP   |      |        |     |     |     | NOP |  |  |  |

|                            | NOP                                                                   | NOP   |      |        |     |     |     | NOP |  |  |  |

|                            | LDW                                                                   | MPYSP | BDEC | FADDSP |     |     |     | LDW |  |  |  |

| K<br>E                     | NOP                                                                   | NOP   | NOP  | NOP    |     |     |     | NOP |  |  |  |

| R                          | NOP                                                                   | NOP   | NOP  | NOP    |     |     |     | NOP |  |  |  |

| N<br>E<br>L                | NOP                                                                   | NOP   | NOP  | NOP    |     |     |     | NOP |  |  |  |

| L                          | NOP                                                                   | NOP   | NOP  | NOP    |     |     |     | NOP |  |  |  |

|                            | NOP                                                                   | NOP   | NOP  | NOP    |     |     |     | NOP |  |  |  |

| E<br>P<br>I<br>L<br>O<br>G |                                                                       | MPYSP |      | FADDSP |     |     |     |     |  |  |  |

|                            |                                                                       | NOP   |      | NOP    |     |     |     |     |  |  |  |

|                            |                                                                       | NOP   |      | NOP    |     |     |     |     |  |  |  |

|                            |                                                                       | NOP   |      | NOP    |     |     |     |     |  |  |  |

|                            |                                                                       |       |      | FADDSP |     |     |     |     |  |  |  |

|                            |                                                                       |       |      | NOP    |     |     |     |     |  |  |  |

|                            |                                                                       |       |      | NOP    |     |     |     |     |  |  |  |

Dans le fichier firtest.h, mettre la macro TEST FIR ASM PIPE à 1

#define TEST\_FIR\_ASM\_PIPE

- Implémenter le code de la fonction fir\_sp\_asm\_softPipeline puis valider son fonctionnement. Cette fonction implémente l'algorithme de filtrage FIR en assembleur C6600 avec optimisation propre aux architectures VLIW et usage optimal du pipeline software d'instructions du CPU (avancement de branche, exécution d'instructions en parallèle, remplacement de NOP, etc). Ne pas oublier les delay slot (NOP) dans votre implémentation.

- Conseils d'implémentation :

- Étape n°1: la profondeur de la boucle kernel interne doit posséder une taille supérieure ou égale au nombre de cycles CPU nécessaires à l'exécution de l'instruction B (branch).

- Étape n°2 : tester la condition de sortie de la boucle ainsi que le bon nombre d'itérations.

- Étape n°3 : vérifier les données préchargées depuis la mémoire par les instructions de chargement sur plusieurs itérations.

- Après validation en mode Debug, lancer une exécution en mode Release, compiler, tester puis reporter les résultats des tests dans le tableau d'analyse comparative ou Benchmarking présent dans le document de Prélude.

- Une fois la mesure réalisée, se remettre en configuration initiale en mode Debug. Toujours garder le mode Debug pour les phases de développement et le mode Release pour les phases de mesure

- Sur CPU VLIW ou EPIC, les NOP's (delay slot) peuvent être vus comme des espaces libres dans lesquels peuvent être insérées des instructions à exécuter en parallèle. Dans une optique de déroulement de boucle, nous pourrons alors être amenés à charger de façon conséquente la boucle kernel actuellement sous exploitée.

- Sans nous en rendre compte, au fil des exercices en assembleur précédents et actuel nous nous efforçons d'entrer dans la tête de notre compilateur C. En effet, lorsque les options d'optimisation sont levées, il tente d'appliquer un maximum des techniques d'accélération que nous sommes en train de découvrir. Sans pour autant obtenir une implémentation optimale. Nous constaterons par la suite que si nous souhaitons obtenir des facteurs d'accélération optimaux après compilation en restant à l'étage du langage C, il nous faudra effectuer du refactoring de code ainsi qu'aiguiller au maximum la chaîne de compilation. Nous perdrons alors en portabilité de code.

15

### 2.6. Vectorisation en assembleur C6600

Nous allons nous intéresser au parallélisme des données en utilisant un maximum d'instructions vectorielles SIMD (Single Instruction Multiple Data) permettant un traitement des opérandes à l'étage assembleur par vecteur de données (2, 4, 8, etc selon la technologie du CPU) et non plus par données scalaires (opérandes traitées une à une). De plus, ceci nous permettra de minimiser l'usage du pipeline logiciel d'instructions et donc le nombre d'unités d'exécution utilisées en parallèle. Nous laisserons ainsi la place potentielle à d'autres instructions. Prenons l'exemple d'une même section de code avec des instructions scalaires et vectorielles. Dans les deux cas, les résultats calculés sont les mêmes et seront stockés dans les mêmes registres CPU. L'implémentation vectorielle est seulement plus rapide.

```

C6600 scalars assembly instructions

C6600 vectorials assembly instructions

(processing time: 18 CPU cycles)

(processing time : 9 CPU cycles)

*A19++, A25

T.DDW

*A19++, A25:A24

NOP

NOP

*A19++, A24

DMPYSP

A25:A24, B23:B22, B5:B4

T.DW

NOP

NOP

MPYSP

A25, B23, B5

NOP

MPYSP

A24, B22, B4

NOP

```

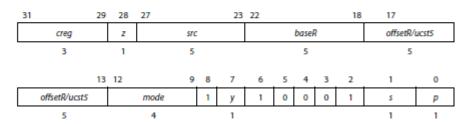

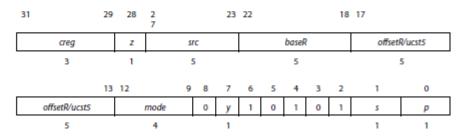

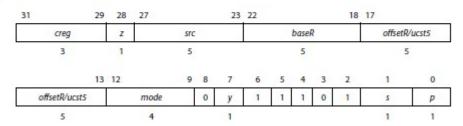

Observons ci-dessous un déroulement d'un facteur 4 (radix 4) de la boucle interne de l'algorithme. La boucle externe reste inchangée et calcule les échantillons de sortie un à un. Dans cet exercice, nous allons implémenter cet algorithme en assembleur C6600 (partie à vectoriser en *gras et italique*). Nous utiliserons les instructions vectorielles suivantes mais sans software pipelining ni optimisation VLIW (ASM C6600 canonique): LDDW, LDNDW, DMPYSP et DADDSP

```

void fir_sp_r14 ( const float * restrict xk,

const float * restrict a,

float * restrict yk,

int na,

int nyk)

int i, j;

float xk0, xk1, xk2, xk3;

float a0, a1, a2, a3;

float acc0, acc1, acc2, acc3;

for (i=0; i< nyk; i++) {

acc0 = 0.0;

acc1 = 0.0;

acc2 = 0.0;

acc3 = 0.0;

for (j=0; j< na; j+=4) {

a0 = a[i];

a1 = a[j+1];

a2 = a[j+2];

a3 = a[j+3];

xk0 = xk[j+i];

xk1 = xk[j+i+1];

xk2 = xk[j+i+2];

xk3 = xk[j+i+3];

acc0 += a0*xk0;

acc1 += a1*xk1;

acc2 += a2*xk2;

acc3 += a3*xk3;

yk[i] = acc0 + acc1 + acc2 + acc3;

}

```

Avant de développer cet algorithme, nous allons analyser le code de base fourni dans la trame pour la fonction fir\_sp\_asm\_r14. Nous le constaterons par nous même par la suite, mais la programmation vectorielle peut être très gourmande en ressources de stockage interne au CPU. Nous allons donc potentiellement avoir besoin de "beaucoup" de registres CPU.

```

save_context

.macro

; save core working registers context on the top of stack

; save Stack Pointer

MV

B15, rsp

STDW

B15:B14, *rsp--[1]

STDW

B13:B12, *rsp--[1]

B11:B10, *rsp--[1]

STDW

A15:A14, *rsp--[1]

STDW

STDW

A13:A12, *rsp--[1]

STDW

A11:A10, *rsp--[1]

ILC, B15

MVC

MVC

RILC, B14

STDW

B15:B14, *rsp--[1]

.endm

restore_context

.macro

rsp

; restore core working registers context from the top of stack

*++rsp[1],B15:B14

LDDW

MVC

B14, RILC

MVC

B15, ILC

LDDW

*++rsp[1],A11:A10

LDDW

*++rsp[1],A13:A12

*++rsp[1],A15:A14

LDDW

*++rsp[1],B11:B10

LDDW

*++rsp[1],B13:B12

LDDW

*++rsp[1],B15:B14

LDDW

; restore Stack Pointer

MV

rsp,B15

NOP

.endm

A3

fir_sp_asm_r14:

save_context

; user code

А3

restore_context

ВЗ

NOP

5

```

- Le compilateur C6600 utilise certains registres CPU pour des usages spécifiques liés au langage C (arguments de fonction, adresse et valeur de retour d'une fonction, etc). En vous aidant de la documentation technique dédiée aux mécanismes d'optimisation sur architectures C6000, préciser les registres utilisés par défaut pour les usages suivants (s'aider de la documentation mentionnée ci-dessous) :

- Arguments de fonction?

- Adresse et valeur de retour d'une fonction ?

- Pointeur SP (Stack Pointer cf. cours Archi. Ordi. 1A)?

- Pointeur FP (Frame Pointer appelé BP ou Base Pointer) ?

- Documentation technique support :

- opt/tp/doc/datasheet

- datasheet optimizing compiler spru187v.pdf

- Chapter 7.3 Register Conventions

- Table 7-2. Register Usage

- La directive préprocesseur assembleur .macro s'utilise comme une macro fonction en langage C (macro avec paramètres). Expliquer le rôle de ces macros dans le programme (s'aider de la documentation mentionnée ci-dessous) ?

- Documentation technique support :

- opt/tp/doc/datasheet

- datasheet assembly tools spru186x.pdf

- Chapter 6 Macro Language Description

- ∘ 6-2. Defining Macros

- Durant l'implémentation de notre algorithme assembleur vectorisé en base 4 (radix 4), quels sont les 5 registres de travail du CPU que nous ne devons en aucun cas utiliser durant la totalité du traitement de la fonction et pourquoi ? Préciser leurs usages spécifiques

- En quoi diffère l'instruction **LDDW** de l'instruction **LDNDW** (s'aider de la documentation mentionnée ci-dessous) ?

- Documentation technique support :

- opt/tp/doc/datasheet

- datasheet instruction set and cpu sprugh7

- Chapter 4 Instructions Descriptions

- Chercher les documentations techniques des 2 instructions ...

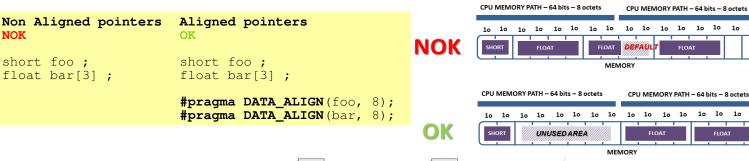

- La page suivante présente succinctement ce qu'est un alignement mémoire!

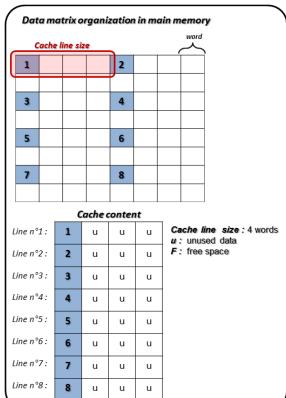

Pour information, le concept d'alignement mémoire des données n'existe que sur processeur à CPU vectoriel et donc des processeurs capables de manipuler les données (lecture/écriture depuis le cache L1D) par paquet (2, 4, 8, etc octets). Prenons ci-dessous un exemple de deux déclarations de deux variables, les premières non-alignées en mémoire et les secondes explicitement alignées modulo 8 octets. Comme pour notre CPU C6600, nous supposerons que les bus entre CPU DSP C6xx (étage d'exécution unités .D1 et .D2) et le niveau mémoire L1D possèdent une taille de 64bits ou 80 (cf. image ci-dessous) :

Vous constaterez que la chaîne de compilation effectue à votre place des alignements mémoire. Vous ne rencontrerez ce type d'optimisation potentielle que sur processeur à CPU vectoriel. Ceci se manifeste par des espaces mémoires vides de quelques octets présents entre vos différentes allocations de structures de données en mémoire. Tout pointeur aligné, possède une valeur multiple de l'alignement réalisé et peut ouvrir l'accès au compilateur à l'utilisation d'instructions de chargement et de sauvegarde mémoire plus rapide en temps d'exécution.

Il s'agit de mécanismes d'optimisation matérielles permettant au CPU de minimiser les accès mémoire aux données. Dans une optique d'optimisation, ceci peut éviter des défauts d'alignement mémoire (programmation vectorielle) et l'utilisation d'instructions dédiées à la lecture/écriture de données alignées (souvent plus lentes). La taille de ces alignements mémoire est le plus souvent liée à la taille d'un mot "vectoriel" CPU. D'une architecture CPU à une autre, cette taille diffère. Sur architecture vectorielle x86/x64 récente, un mot CPU fait 128bits (160) depuis l'arrivée des extensions SIMD SSE (chemins/bus larges vers la mémoire donnée L1D). Les alignements mémoire de structures de données se feront donc le plus souvent via des adresses de valeurs multiples de 16 (modulo 160). En résumé, la taille d'un mot vectoriel CPU dépend :

- Taille des path vers la mémoire donnée de niveau 1 ou L1D (le plus souvent un cache) : Exemple de la famille coreiX sandyBridge, 128bits vers le cache programme L1P, 2x128bits load et 1x128bits store vers le cache donnée L1D

- Taille des lignes de cache (tailles multiples d'un mot vectoriel CPU)

Dans le fichier firtest.h, mettre la macro TEST\_FIR\_ASM\_R4 à 1

### #define TEST\_FIR\_ASM\_R4 1

- Implémenter le code de la fonction fir\_sp\_asm\_r14 puis valider son fonctionnement. Cette fonction implémente l'algorithme de filtrage FIR en assembleur C6600 sans optimisation propre aux architectures VLIW mais avec usage d'instructions vectorielles C6600. Ne pas oublier les delay slot (NOP) dans votre implémentation. Utiliser les instructions suivantes :

- LDDW

- LDNDW

- DMPYSP

- DADDSP

- Quelle limitation d'usage amène l'implémentation de notre algorithme de filtrage?

- Après validation en mode Debug, lancer une exécution en mode Release, compiler, tester puis reporter les résultats des tests dans le tableau d'analyse comparative ou Benchmarking présent dans le document de Prélude.

- Une fois la mesure réalisée, se remettre en configuration initiale en **mode Debug**. Toujours garder le mode Debug pour les phases de développement et le mode Release pour les phases de mesure

Voilà, à ce stade là de la formation en systèmes embarqués, vous devez être apte à porter un esprit critique sur les performances annoncées d'un processeur et ne plus regarder que sa seule fréquence de travail. Un processeur, même mono-cœur, cadencé à 500MHz peut très bien offrir des performances supérieures à un processeur multi-coeurs cadencé à 2GHz. Pour une architecture mono-cœur voire multi-coeurs. Il vous faut notamment tenir compte :

- de sa faculté à traiter des instructions en parallèle (nombre d'unités d'exécution pouvant travailler simultanément, largeur des bus entre cache L1P et étage de FETCH du CPU, etc)

- de sa faculté à traiter les données en parallèle (largeur des bus cache L1D et étage d'exécution du CPU, largeur des registres de travail vectoriels du CPU, jeu d'instructions vectorielles, etc)

- de la technologie de son pipeline matériel (superscalaire, VLIW ou EPIC), voire pour les plus curieux, des stratégies d'accélération interne au pipeline (le plus souvent aux étages de décodage et d'exécution)

#### 2.7. Déroulement de boucle en C canonique

A partir de maintenant, la totalité de nos développements se feront en langage C. Nous découvrirons dans un premier temps des stratégies simples d'optimisation portables et applicables à beaucoup de processeurs vectoriels. Nous conclurons par une stratégie d'accélération optimale pour notre architecture mais amenant son lot d'inconvénients.

Le principe du déroulement de boucle consiste, sans mécanisme d'optimisation particulier, de ré-implémenter en C canonique notre algorithme en doublant/quadruplant/etc le nombre de chargement mémoire, d'opérations arithmétiques, etc dans nos boucles. Prenons un exemple cidessous de déroulement de boucle d'un facteur 2, souvent nommé unrolling radix 2 ou déroulement en base 2 :

#### Canonical C Canonical C with unrolling radix 2 float \* restrict pYk, float \* restrict pYk, int nbCoeff) int nbCoeff) { int i; int i; float $yk\_tmp = 0.0f;$ float xk\_tmp1, xk\_tmp2; float a\_tmp1, a\_tmp2; float mul1, mul2; float add1 = 0.0f, add2 = 0.0f; for (i=0; i<nbCoeff; i++) {</pre> $yk_tmp += a[i]*xk[i];$ for (i=0; i<nbCoeff; i+=2) {</pre> $xk_tmp1 = xk[i];$ $*pYk = yk_tmp;$ $xk_tmp2 = xk[i+1];$ a tmp1 = a[i]; $a_{tmp2} = a[i+1];$ mul1 = a\_tmp1 \* xk\_tmp1; mul2 = a\_tmp2 \* xk\_tmp2; add1 += mul1; add2 += mul2; \*pYk = add1 + add2;

• Dans le fichier firtest.h, mettre la macro TEST FIR SP R4 à 1

#### #define TEST\_FIR\_SP\_R4 1

- Implémenter le code de la fonction fir\_sp\_r4 puis valider son fonctionnement. Cette fonction implémente l'algorithme de filtrage FIR en C canonique avec déroulement des 2 boucles interne et externe d'un facteur 4 (radix 4).

- Quelle limitation d'usage amène l'implémentation de notre algorithme de filtrage?

- Après validation en mode Debug, lancer une exécution en mode Release, compiler, tester puis reporter les résultats des tests dans le tableau d'analyse comparative ou Benchmarking présent dans le document de Prélude.

- Une fois la mesure réalisée, se remettre en configuration initiale en mode Debug. Toujours garder le mode Debug pour les phases de développement et le mode Release pour les phases de mesure

#### 2.8. Vectorisation en C intrinsèque

Durant cet exercice, nous allons réutiliser la totalité de nos anciens acquis afin d'obtenir une implémentation optimale de notre algorithme de filtrage. Nous allons comprendre que les étapes précédentes, même si contre-performantes au seul regard des Benchmarking, étaient nécessaires à une bonne compréhension des stratégies présentées ci-dessous. Afin, d'exploiter au mieux l'architecture matérielle parallèle, vectorielle, VLIW de chaque cœur, sans pour autant descendre à l'étage assembleur qui peut être très chronophage en temps de développement, nous allons devoir aiguiller au maximum notre chaîne de compilation en effectuant du refactoring de code.

Découvrons quelques une des techniques les plus efficaces pour maîtriser la totalité du potentiel d'optimisation de notre chaîne de compilation (s'aider de la documentation mentionnée ci-dessous). Lire également la page suivante :

- opt/tp/doc/datasheet

- datasheet optimizing compiler spru187v.pdf

- Chapter 7.5.6 Using intrinsics to Access Assembly Langage Statements

| Examples of C intrinsics functions                          | C6600 assembly equivalence                                   |

|-------------------------------------------------------------|--------------------------------------------------------------|

| for C6600 compiler and architecture                         | (automatic register allocation by compiler)                  |

| //float2_t container type for 2 floats                      |                                                              |

| float2_t data10;<br>const float ldData[2] = {0.0f,1.0f};    | ; data10 = A1:A0<br>; &ldData[0] = ldData = A2               |

| <pre>data10 = _amemd8_const(&amp;ldData[0]);</pre>          | <b>LDDW</b> *A2, A1:A0                                       |

| <pre>float2_t data10, data32;float2_t result31_20;</pre>    | ; data10 = A1:A0, data32 = A3:A2,<br>; result31_20 = A11:A10 |

| result31_20 = <b>_daddsp</b> (data10, data32);              | <b>DADDSP</b> A1:A0, A3:A2, A11:A10                          |

| float2_t data10, data32;<br>float2_t result31_20;           | ; data10 = A1:A0, data32 = A3:A2,<br>; result31_20 = A11:A10 |

| result31_20 = <b>_dmpysp</b> (data10, data32);              | DMPYSP A1:A0, A3:A2, A11:A10                                 |

| <pre>float2_t data10;float2_t data32;float2_t data21;</pre> | ; data32 = A3:A2<br>; data10 = A1:A0<br>; data21= A11:A10    |

| <pre>data21 = _ftod(_lof(data32), _hif(data10));</pre>      | MV A2, A11<br>MV A1, A10                                     |

| float2_t data10;<br>float stData[2];                        | ; data10 = A1:A0<br>; &stData[0] = stData = A2               |

| _amemd8(&stData[0]) = data10;                               | <b>STDW</b> A1:A0, *A2                                       |

Les fonctions intrinsèques ou intrinsics sont dépendantes de l'architecture CPU cible. Elles existent principalement sur processeur vectoriel. D'une architecture CPU et donc d'une chaîne de compilation à une autre, la prise en main de la nouvelle API (Application Programming Interface) intrinsics est nécessaire.

A l'image d'une fonction inline, une fonction intrinsèque force le compilateur à générer automatiquement une séquence d'instructions. Cependant, contrairement aux fonctions inlines, le compilateur possède une connaissance poussée de la fonction intrinsèque qui lui assure une insertion optimale pour un contexte donné.

Observons un exemple de comparaison entre une implémentation C canonique et une solution avec fonctions intrinsèques. \_\_float2\_t est un type conteneur (container type) sur 64bits et pouvant contenir 2 flottants en simple précision sur 32 bits :

| Canonical C example                                                           | Example of C intrinsic function                                                   |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| <pre>float data[2] = {0.0f, 1.0f}; float data0, data1;</pre>                  | <pre>const float data[2] = {0.0f, 1.0f};float2_t data10;</pre>                    |

| <pre>// 2 x LDW assembly instructions data0 = data[0]; data1 = data[1];</pre> | <pre>// 1 x LDDW assembly instruction data10 = _amemd8_const(&amp;data[0]);</pre> |

• Assertion: l'objectif de cette technique est de donner un maximum d'informations (écrites et garanties par le développeur) sur une variable pour la chaîne de compilation afin de l'aiguiller dans ses phases d'optimisation futures. Par exemple, nous pouvons spécifier à la toolchain sa valeur minimale, si la valeur d'une variable est toujours multiple d'une autre valeur, l'alignement mémoire de données, etc

| Example of program with assertions                                                              | Description                                                                                                                     |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| <pre>short i, size=4; const float data[4] = {0.0f, 1.0f, 2.0f, 3.0f};float2_t acc = 0.0f;</pre> |                                                                                                                                 |

| <pre>#pragma DATA_ALIGN(data, 8);</pre>                                                         | <ul> <li>Force l'édition des liens<br/>(linking) à aligner en<br/>mémoire les données du<br/>tableau data[] modulo 8</li> </ul> |

| <pre>_nassert(size &gt;= 2); _nassert(size % 2 == 0); _nassert((int) data % 8 == 0);</pre>      | <ul> <li>octets</li> <li>size est forcément supérieur ou égal à 2</li> </ul>                                                    |

| <pre>for (i=0; i<size; i+="2)" pre="" {<=""></size;></pre>                                      | <ul> <li>size est forcément un<br/>multiple de 2</li> </ul>                                                                     |

| <pre>acc =_daddsp (acc, _amemd8_const(&amp;data[i]); }</pre>                                    | <ul> <li>L'adresse de base du tableau<br/>data possède une valeur<br/>multiple de 8 (pointeur<br/>modulo 8 octets)</li> </ul>   |

Alignement mémoire: dans l'exemple ci-dessus, la directive de compilation #pragma DATA\_ALIGN force l'édition des liens ou linking à garantir un alignement mémoire modulo 8 octets des données visées par le pointeur passé en argument. Prenons un exemple d'alignement mémoire de données modulo 8 octets sur chaîne de compilation:

```

/* arrays alignments - CPU data path length 64bits */

#pragma DATA_ALIGN(xk_sp, 8);

```

Dans l'exemple de code avec assertions et alignement mémoire ci-dessus, que vaut la variable de type conteneur acc après exécution de la boucle?

- Implémenter le code de la fonction fir\_sp\_opt\_r4 puis valider son fonctionnement. Cette fonction implémente l'algorithme de filtrage FIR en C intrinsèque C6600 avec déroulement des 2 boucles interne et externe d'un facteur 4 (radix 4).

- Quelle limitation d'usage amène l'implémentation de notre algorithme de filtrage ?

- Après validation en mode Debug, lancer une exécution en mode Release, compiler, tester puis reporter les résultats des tests dans le tableau d'analyse comparative ou Benchmarking présent dans le document de Prélude.

- Une fois la mesure réalisée, se remettre en configuration initiale en **mode Debug**. Toujours garder le mode Debug pour les phases de développement et le mode Release pour les phases de mesure

- En vous aidant de l'annexe 1, générer une bibliothèque statique nommée **firlib.a** et la placer dans le répertoire **/disco/c6678/firlib/lib/**. Tester votre bibliothèque statique binaire avec votre projet de test.

- Voilà, à ce stade nous venons d'effectuer une implémentation optimale de notre algorithme pour notre DSP VLIW C6600. Porter un regard critique sur nos développements et citer les avantages et inconvénients de l'algorithme final

- L'exécution de l'algorithme tel qu'il a été écrit mathématiquement dans sa forme initiale ne peut pas être plus accélérée dans une optique de vectorisation en C sur notre architecture. Si nous souhaitons améliorer le temps de calcul de notre produit scalaire, il nous faudrait alors réduire sa complexité Mathématique en nombre de MACS. Les transformations à apporter ne seraient donc plus d'ordre technologique dans un premier temps, mais d'ordres mathématique et théorique. Une fois ces transformations appliquées, nous pourrions alors repasser sur des phases d'optimisation architectures dépendantes telles que celles présentées dans ce chapitre.

- De plus, nous venons de le constater, du moment que nous avons une connaissance poussée de l'architecture, du jeu d'instructions et de notre chaîne de compilation, développer des bibliothèques spécialisées en assembleur peut s'avérer contre-productif au regard du ratio performance/effort. Ceci sera vrai sur toute architecture VLIW, EPIC et superscalaire, du moment que l'étage d'optimisation de la toolchain reste un minimum performant.

notes

©creative ©Commons

# TRAVAUX PRATIQUES

PROGRAMMATION VECTORIELLE SUR GPP INTEL x86\_64

# ARCHITECTURES POUR LE CALCUL

#### SOMMAIRE

- 3. PROGRAMMATION VECTORIELLE SUR GPP INTEL x86\_64

- 3.1. Analyse du programme de test3.2. Vectorisation avec ISA extension SSE4.13.3. Synthèse

#### 3.1. Analyse du programme de test

VS

Nous allons effectuer un Benchmarking entre architectures processeurs en mettant en confrontation une architecture superscalaire GPP (General Purpose Processor) Intel corei7 en micro-architecture Haswell cadencée à 3,6GHz (machines de TP en salles A203/A201) et notre architecture DSP VLIW C6600 cadencée à 1,4GHz proposée par Texas Instruments. Notre première comparaison se fera sur une implémentation en C canonique.

Intel corei7 - 4790 Haswell 4<sup>th</sup> gen

3,6GHz, 105W en charge prix unitaire : 325€ (en 2015) Texas Instruments TMS320C6678

1,4GHz, 10W en charge prix unitaire : 240€ (160€ pour 1Ku)

• Ouvrir un **shell** et se déplacer dans le répertoire de travail **disco/ia64**. Afficher et analyser le contenu du fichier **README.md** à la racine. Compiler le projet et analyser les fichiers de test et résultats.

<your\_computer\_path>/disco/ia64\$ make

<your\_computer\_path>/disco/ia64\$ ./build/bin/firtest

• Exécuter plusieurs fois d'affilée le programme de test et observer les mesures de l'algorithme. Que constatez-vous ?

Nous pouvons constater qu'une implémentation en C canonique, même avec déroulement de boucle, garantit une portabilité du code, même sur des architectures matérielles différentes. Nous constatons également, que contrairement au CPU VLIW d'un DSP C6600, les CPU superscalaires des GPP x86\_64 ne sont pas déterministes et donc ''potentiellement'' moins adaptés aux applications temps réel imposant des contraintes dures. Ceci est principalement lié aux étages suivants :

- Technologie du pipeline superscalaire (exécution Out-Of-Order, prédiction, spéculation, etc)

- Utilisation d'un modèle mémoire pleinement cachable pour les niveaux L1/L2/L3

- Utilisation d'une **MMU** (Memory Management Unit) pour la translation d'adresses virtuelles en adresses physiques (Table de translation, TLB, etc)

- Au côté multi-applicatif du système de la machine de test. De plus, Linux comme le noyau de Windows ne sont pas des kernels temps réel (scheduler non déterministe). En effet, bien d'autres programmes de même privilège sont en cours d'exécution sur l'ordinateur de développement (exécuter l'utilitaire htop pour observer en temps réel les processus et threads en cours d'exécution)

notes

- Dans le **Makefile**, nous pouvons observer que des options de compilation spécifiques sont passées à GCC. A quoi correspondent les 3 options suivantes (s'aider de *man gcc* et d'internet):

- · -03

- ∘ -std=c99

- -march=native

```

CFLAGS = -Wall -march=native -std=c99 -O3

```

• Dans le fichier disco/ia64/test/src/main.c, nous pouvons observer la définition d'une fonction inline, dans notre cas implémentée en C avec insertion d'une séquence en assembleur 64bits x86\_64. Cette fonction force le CPU courant à vider son pipeline matériel puis réalise une lecture de la valeur courante du core timer TSC (timer présent dans chaque CPU), comme précédemment sur architecture C6600. Sur architectures compatibles x86-x64, ce timer 64bits est démarré à la mise sous tension de la machine et compte jusqu'à débordement. En vous aidant d'internet, rappeler le rôle du spécificateur inline, préciser l'intérêt et donner des exemples d'utilisation ?

```

inline unsigned long long __attribute__((always_inline)) rdtsc_inline()

unsigned int hi, lo;

"cpuid\n\t"

// read current TSC value

"rdtsc"

: "=a"(lo), "=d"(hi)

: // no parameters

: "rbx", "rcx");

return ((unsigned long long)hi << 32ull) | (unsigned long long)lo;

}

. . .

start = rdtsc_inline();

fir_sp (xk_sp, a_sp, yk_sp_cn, A_LENGTH, YK_LENGTH);

stop = rdtsc_inline();

duration = stop - start;

. . .

```

- Quelles sont les principales différences entre une fonction **inline** et une fonction **intrinsèque** (s'aider d'internet)?

- Reporter les résultats des tests dans le tableau d'analyse comparative ou Benchmarking présent dans le document de Prélude. Prendre une moyenne de 10 mesures. Vous pouvez programmer la boucle de test si vous le souhaitez.

#### 3.2. Vectorisation avec ISA extension SSE4.1

Nous allons maintenant comparer ce qui peut être comparable, à savoir les performances de notre code vectorisé sur architecture C6600 à du code vectorisé sur architecture IA-64. Nous nous intéresserons notamment à l'extension vectorielle SIMD SSE4.1 proposée par Intel. Pour information, courant 2014, Intel proposa sur sa micro-architecture Haswell une extension DSP (Digital Signal Processing). Cette extension, nommée FMA (Fused Multiply-Add), est donc dédiée aux applications de traitement numérique du signal mais ne sera néanmoins pas abordée en travaux pratiques. Pour les plus curieux, ne pas hésiter à aller voir sur MSDN (MicroSoft Developer Network) les quelques fonctions intrinsèques proposées.

Cette partie n'a pas vocation à permettre de découvrir en profondeur l'architecture interne des processeurs compatibles x86\_64 (Intel ou AMD), notamment les architectures Intel. Néanmoins, nous allons pouvoir constater que nos précédents acquis nous permettent maintenant d'effectuer de la vectorisation de code sur toute architecture vectorielle processeur. Les concepts resteront le plus souvent les mêmes. Avant tout, nous avons à savoir que les architectures x86\_64 actuelles possèdent plusieurs banques de registres vectoriels :

- Registres MMX 64bits : peuvent contenir jusqu'à 2 flottants 32bits

- Registres XMM 128bits : peuvent contenir jusqu'à 4 flottants 32bits

- Registres YMM 256bits : peuvent contenir jusqu'à 8 flottants 32bits

Dans notre cas, les instructions de l'extension SSE4.1 travaillent avec les registres XMM 128bits et sont aptes à manipuler les flottants en simple précision (IEEE-754) par paquets de 4. Le type conteneur \_\_m128 permet donc de stocker jusqu'à 4 flottants en simple précision :

Container type (4 x 32bits floating point) : \_\_m128

https://msdn.microsoft.com/fr-fr/library/y0dh78ez(v=vs.90).aspx

• Observons les préfixations et suffixations des fonctions intrinsèques présentées dans la suite de cet exercice :

Intel x86\_64 Intrinsic syntax: \_mm\_<intrinsic\_name>\_<data\_type>

• Mise à zéro des éléments d'un vecteur de flottants. Pour information, **ps** signifie **Packet Single**, soit paquet de flottants en simple précision 32bits IEEE754 :

```

__m128 float_vector;

float_vector = _mm_setzero_ps ();

```

https://msdn.microsoft.com/fr-fr/library/tk1t2tbz(v=VS.90).aspx

Initialise les éléments d'un vecteur de flottants :

```

__m128 float_vector;

float_vector = _mm_set_ps (1.0, 2.2, 3.0, 7.0);

```

#### https://msdn.microsoft.com/fr-fr/library/afh0zf75(v=vs.90).aspx

• Chargement d'un vecteur de 4 flottants **alignés** depuis la mémoire vers un registre XMM de destination :

```

float tab[4] = {1.0, 3.4, 5.0, 6.0};

__m128 float_vector;

float_vector = _mm_load_ps (&tab[0]);

```

#### https://msdn.microsoft.com/fr-fr/library/zzd50xxt(v=vs.90).aspx

• Chargement d'un vecteur de 4 flottants **non-alignés** depuis la mémoire vers un registre XMM de destination :

```

float tab[4] = {1.0, 3.4, 5.0, 6.0};

__m128 float_vector;

float_vector = _mm_loadu_ps (&tab[0]);

```

#### https://msdn.microsoft.com/fr-fr/library/x1b16s7z(v=vs.90).aspx

• Produit scalaire entre deux vecteurs de 4 flottants (result = a0.x0 + a1.x1 + a2.x2 + a3.x3). Le résultat du produit scalaire est un nombre scalaire, le résultat est par défaut sauvé dans les 32bits de poids faible du vecteur 128bits de destination:

```

__m128 float_vector_src1;

__m128 float_vector_src2;

__m128 float_vector_dst;

float_vector_dst = _mm_dp_ps (float_vector_src1, float_vector_src2, 0xff);

```

#### https://msdn.microsoft.com/fr-fr/library/bb514054(v=vs.90).aspx

Addition de deux vecteurs contenant 4 flottants chacun :

```

__m128 float_vector_src1;

__m128 float_vector_src2;

__m128 float_vector_dst;

float_vector_dst = __mm_add_ps (float_vector_src1, float_vector_src2);

```

https://msdn.microsoft.com/fr-fr/library/c9848chc(v=vs.90).aspx

Sauvegarde en mémoire d'un vecteur de 4 flottants alignés :

```

float tab[4];

__m128 float_vector;

float_vector = _mm_set_ps (1.0, 2.2, 3.0, 7.0);

_mm_store_ps (&tab[0], float_vector);

```

#### https://msdn.microsoft.com/fr-fr/library/s3h4ay6y(v=vs.90).aspx

• Ouvrir le fichier /disco/ia64/firlib/h/firlib.h et observer les déclarations de type et d'union présentées ci-dessous. Cette union, greffée à une déclaration de type, permet, après déclaration d'une variable conteneur, d'accéder à un vecteur XMM soit élément par élément, soit directement au vecteur 128bits complet. En vous aidant d'internet, rappeler ce qu'est une union et préciser la différence avec une structure ?

Dans l'exemple ci-dessous, comment accéder au 3<sup>ième</sup> élément de la variable vectorielle data\_vec de type conteneur XMM 128bits.

```

xmm_t data_vec;

```

- Ouvrir le fichier /disco/ia64/firlib/src/fir\_sp\_sse\_r4.c puis implémenter le code vectorisé pour architecture x64 correspondant à la fonction fir\_sp\_r4. Valider son bon fonctionnement sans oublier de vérifier l'alignement mémoire des différents vecteurs de données traités par l'algorithme.

- Reporter les résultats des tests dans le tableau d'analyse comparative ou Benchmarking présent dans le document de Prélude. Prendre une moyenne de 10 mesures. Vous pouvez programmer la boucle de test si vous le souhaitez.

#### 3.3. Synthèse