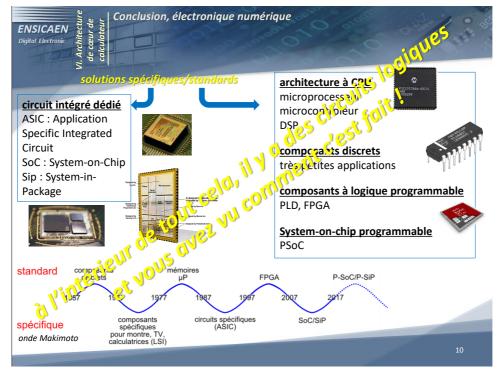

# Electronique numérique Circuits et architectures logiques 2025-2026 – 1A ELEC

M.Denoual

#### ENSICAEN

1

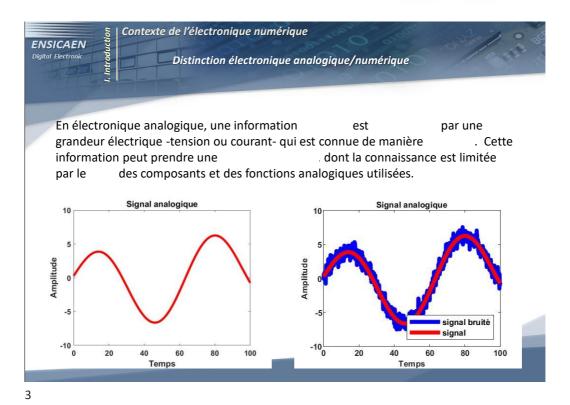

Contexte de l'électronique numérique **ENSICAEN** Distinction électronique analogique/numérique Les domaines d'application de l'électronique analogique ont tendance à se réduire au profit de l'électronique numérique. Les 3 domaines restants d'applications de l'électronique analogique sont: 1. le conditionnement de signaux issus de capteurs (amplification et filtrage). L'objectif est alors de dégager un signal électrique souvent faible du bruit de façon à pouvoir l'utiliser ou le traiter. numérisation amplification capteui filtrage physique Remarques : - Toutes les grandeurs physiques sont analogiques - Dans certains capteurs récents, on peut trouver des électroniques de numérisation directe sur puce qui repoussent encore le domaine de l'analogique.

- 2. communication radio-fréquence (RF) ou électronique haute-fréquence

- 3. électronique de puissance

### Rmq 1

#### Remarques :

- On trouve également de l'électronique analogique dans les systèmes automatiques pour l'asservissement ou la régulation.

Mais la tendance générale en automatique est le développement à partir d'électronique numérique. Cette tendance est soutenue par les capacités croissant sans cesse des composants numériques (vitesse, capacité de calcul) et par la diminution de leur coût.

- L'électronique analogique peut présenter un intérêt pour des dispositifs peu complexes et faible coût.

5

5

6

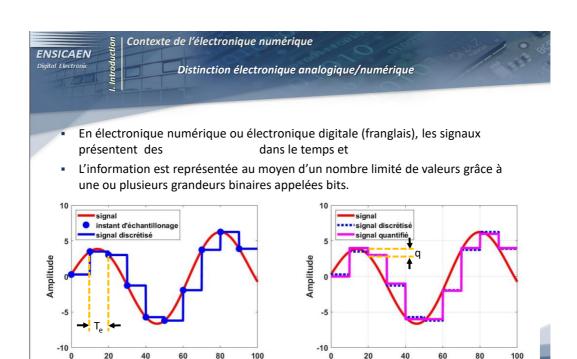

Temps

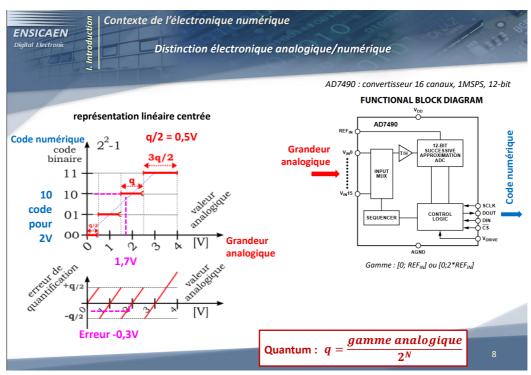

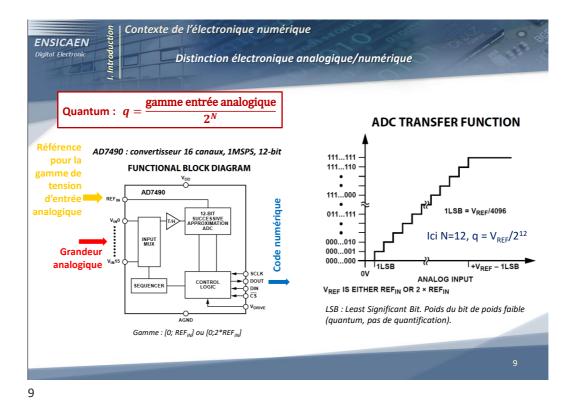

q : quantum, pas de quantification

Temps

T<sub>e</sub> : période d'échantillonnage

Contexte de l'électronique numérique **ENSICAEN** Signaux numériques valeur contexte vrai/faux logique bits: binary digit (chiffre binaire) Ces bits prennent les valeurs : 0/1 logique booléenne TRUTH TABLE l<sub>2</sub> 01 L 0V/5V aspect électrique Н Н L  $^{1}\!/_{4}$  of device shown Н Н  $J=\overline{A+B}$ Н Н Logical "1" = HIGH L/H datasheet Logical "0" = LOW H = HIGH state (the more positive voltage) L = LOW state (the less positive voltage) All inputs protected by standard 5V/0V logique négative CMOS protection circuit. table de vérité dans une datasheet de relation entre valeur 12V/-12V transmission série composant logique discret logique et niveau électrique dans une datasheet de composant logique discret

Exemples de signaux numériques

- bouton poussoir (touche d'un clavier):

BP=1, bouton enfoncé, interrupteur fermé

BP=0, bouton relâché, interrupteur ouvert

- lampe : L=1, lampe allumée / L=0, lampe éteinte

- pixel d'une image (télévision numérique)

- diffusion : bits

Smart Watch et autres petits écran format image RGB565 16 bits

Question: combien de couleur peut-on coder en format diffusion?

12

12

? Questions :

Combien de valeurs peut-on représenter avec N de bits ?

Quelle est l'erreur de quantification maximum en fonction du quantum?

On suppose une gamme de tension de [0-4V] et 2 bits de représentation, combien valent le quantum (pas de quantification) et l'erreur maximum de représentation ?

Application numérique pour N=10 bits et une gamme de tension [0-5V]

13

Question : quelle taille mémoire pour 1 heure de musique, stéréo non compressée ?

- Signal numérisé sortant d'un capteur : 8 à 12 bits. Exemple, capteur de température DS18P20 : 10 bits

- Code ASCII: bits ( caractères)

(American Standard Code for Information Interchange)

14

14

| ISICA<br>tal Elect | receipt in |           | I. Introduction |          | F     | F        |          | Sign   | aux n   | umériq       |   |     | 0   |        | 6   | <        | 0          |     |     |              |     | S.       |   |

|--------------------|------------|-----------|-----------------|----------|-------|----------|----------|--------|---------|--------------|---|-----|-----|--------|-----|----------|------------|-----|-----|--------------|-----|----------|---|

| ecimal             | Hex        | ASCII     | Decimal         | Hex      | ASCII | Decimal  | Hex      | ASCII  | Decimal | Hex ASC      |   | Dec | Hex | Char   | Dec | Hex      | Char       | Dec | Hex | Char         | Dec | Hex      | 1 |

| 0                  | 0          | NUL       | 32              | 20       |       | 64       | 40       | æ      | 96      | 60 .         |   | 128 | 80  | Ç      | 160 | A0       | a          | 192 | C0  | L            | 224 | E0       |   |

| 1                  | 1          | SOH       | 33              | 21       |       | 65       | 41       | Α      | 97      | 61 a         |   | 129 | 81  | ļ ų    | 161 | A1       | i          | 193 | C1  | ‡            | 225 | E1       |   |

| 2                  | 2          | STX       | 34              | 22       |       | 66       | 42       | В      | 98      | 62 b         |   | 130 | 82  | e<br>â | 162 | A2       | ó          | 194 | C2  | Ţ            | 226 | E2       |   |

| 3                  | 3          | ETX       | 35              | 23       | #     | 67       | 43       | С      | 99      | 63 c         |   | 131 | 83  | **     | 163 | A3       | ú          | 195 | C3  |              | 227 | E3       |   |

| 4                  | 4          | EOT       | 36              | 24       | \$    | 68       | 44       | D      | 100     | 64 d         |   | 132 | 84  | a      | 164 | A4       | Ñ          | 196 | C4  | <del>-</del> | 228 | E4       | ı |

| 5                  | 5          | ENQ       | 37              | 25       | %     | 69       | 45       | E      | 101     | 65 e         |   | 133 | 85  | a      | 165 | A5       |            | 197 | C5  | IT I         | 229 | E5       | ı |

| 6                  | 6          | ACK       | 38              | 26       | &     | 70       | 46       | F      | 102     | 66 f         |   | 134 | 86  | ç      | 166 | A6<br>A7 | 0          | 198 | C6  | 111          | 230 | E6<br>E7 | ı |

| 7                  | 7          | BEL       | 39              | 27       |       | 71       | 47       | G      | 103     | 67 g         |   | 136 | 88  | ê      | 168 | A8       | ž          | 200 | C8  | [ [          | 232 | E8       | ı |

| 8                  | 8          | BS        | 40              | 28       | (     | 72       | 48       | Н      | 104     | 68 h         |   | 137 | 89  | ë      | 169 | A9       | -          | 200 | C9  | L<br>F       | 232 | E9       | l |

| 9                  | 9          | HT        | 41              | 29       | )     | 73       | 49       |        | 105     | 69 i         |   | 138 | 8A  | è      | 170 | AA       | -          | 201 | CA  | L I          | 234 | EA       | l |

| 10                 | Α          | LF        | 42              | 2A       | ^     | 74       | 4A       | J      | 106     | 6A j         |   | 139 | 88  | ï      | 171 | AB       |            | 203 | CB  | T            | 235 | EB       | ı |

| 11                 | В          | VT        | 43              | 2B       | +     | 75       | 4B       | K      | 107     | 6B k         |   | 140 | 8C  | î      | 172 | AC       | 1/2<br>1/4 | 204 | CC  | i i          | 236 | EC       | ı |

| 12                 | С          | FF        | 44              | 2C       | ,     | 76       | 4C       | L      | 108     | 6C I         |   | 141 | 8D  | ì      | 173 | AD       | 4          | 205 | CD  | <u> </u>     | 237 | ED       | П |

| 13                 | D          | CR        | 45              | 2D       | -     | 77       | 4D       | M      | 109     | 6D m         |   | 142 | 8E  | Ä      | 174 | AE       | «          | 206 | CE  | +            | 238 | EE       | ı |

| 14                 | E<br>F     | SOH       | 46              | 2E       | 7     | 78       | 4E       | N<br>O | 110     | 6E n         |   | 143 | 8F  | Å      | 175 | AF       | »          | 207 | CF  | <u>   </u>   | 239 | EF       | ı |

| 16                 | 10         | SI<br>DLE | 48              | 2F<br>30 | 0     | 79<br>80 | 4F<br>50 | P      | 111     | 6F 0         |   | 144 | 90  | É      | 176 | ВО       | iii        | 208 | DO  | 1            | 240 | FO       | l |

| 17                 | 11         | DC1       | 49              | 31       | 1     | 81       | 51       | 0      | 113     | 70 p         |   | 145 | 91  | æ      | 177 | B1       | ì          | 209 | D1  | <del>-</del> | 241 | F1       | ı |

| 18                 | 12         | DC2       | 50              | 32       | 2     | 82       | 52       | R      | 114     | 71 q<br>72 r |   | 146 | 92  | Æ      | 178 | B2       | m          | 210 | D2  |              | 242 | F2       | П |

| 19                 | 13         | DC3       | 51              | 33       | 3     | 83       | 53       | S      | 115     | 73 s         | 1 | 147 | 93  | ô      | 179 | В3       | ΙŦΙ        | 211 | D3  | T            | 243 | F3       | П |

| 20                 | 14         | DC4       | 52              | 34       | 4     | 84       | 54       | T      | 116     | 74 t         | 1 | 148 | 94  | ö      | 180 | B4       | ы          | 212 | D4  | 1            | 244 | F4       | П |

| 21                 | 15         | NAK       | 53              | 35       | 5     | 85       | 55       | Ü      | 117     | 75 u         | 1 | 149 | 95  | ò      | 181 | B5       | 14         | 213 | D5  | F            | 245 | F5       |   |

| 22                 | 16         | SYN       | 54              | 36       | 6     | 86       | 56       | v      | 118     | 76 v         | 1 | 150 | 96  | û      | 182 | В6       | 14 1       | 214 | D6  | l ir l       | 246 | F6       | ı |

| 23                 | 17         | ETB       | 55              | 37       | 7     | 87       | 57       | w      | 119     | 77 w         | 1 | 151 | 97  | ù      | 183 | В7       | i          | 215 | D7  | +            | 247 | F7       | ı |

| 24                 | 18         | CAN       | 56              | 38       | 8     | 88       | 58       | X      | 120     | 78 x         | 1 | 152 | 98  | ÿ      | 184 | B8       | 7          | 216 | D8  | <del> </del> | 248 | F8       | l |

| 25                 | 19         | EM        | 57              | 39       | 9     | 89       | 59       | Y      | 121     | 79 y         | 1 | 153 | 99  | Ö      | 185 | В9       | -          | 217 | D9  |              | 249 | F9       |   |

| 26                 | 1A         | SUB       | 58              | 3A       | :     | 90       | 5A       | Z      | 122     | 7A z         | 1 | 154 | 9A  | Ü      | 186 | BA       |            | 218 | DA  | ı            | 250 | FA       |   |

| 27                 | 1B         | ESC       | 59              | 3B       | ;     | 91       | 5B       | 1      | 123     | 7B {         | 1 | 155 | 9B  | ¢      | 187 | ВВ       | i          | 219 | DB  |              | 251 | FB       |   |

| 28                 | 1C         | FS        | 60              | 3C       | <     | 92       | 5C       | 1      | 124     | 7C           | 1 | 156 | 9C  | £      | 188 | BC       | 1          | 220 | DC  | ļ .          | 252 | FC       |   |

| 29                 | 1D         | GS        | 61              | 3D       | =     | 93       | 5D       | 1      | 125     | 7D }         |   | 157 | 9D  | ¥      | 189 | BD       | J          | 221 | DD  | II, I        | 253 | FD       | l |

| 30                 | 1E         | RS        | 62              | 3E       | >     | 94       | 5E       | ^      | 126     | 7E ~         |   | 158 | 9E  | Pt     | 190 | BE       | ]          | 222 | DE  |              | 254 | FE       |   |

| 31                 | 1F         | US        | 63              | 3F       | ?     | 95       | 5F       |        | 127     | 7F 🗆         |   | 159 | 9F  | f      | 191 | BF       | ٦          | 223 | DF  |              | 255 | FF       |   |

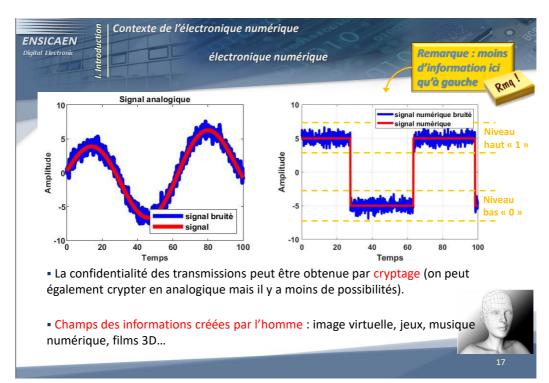

- L'électronique numérique est particulièrement adaptée aux calculs et aux tests.

- Ces calculs et tests sont la base des algorithmes de traitement par exemple en traitement numérique du signal (TNS) pour le filtrage, pour le cryptage ou la commande de procédé.

Rmq!

**Remarque :** en électronique analogique, la seule façon de faire des calculs est d'utiliser des amplificateurs opérationnels (d'où le nom).

- Les signaux numériques présentent en outre la possibilité d'être compressés (codage MP3, zip) et stockés longtemps.

- D'un point de vue transmission et également stockage et traitement, les informations numériques présentent une meilleure immunité au bruit. Cette caractéristique est très utile pour les communications pour réduire le taux d'erreur et peut être accrue par un codage (code correcteur d'erreur).

16

18

- Qu'est-ce qu'un signal quantifié ?

- Quels intérêts à utiliser des signaux numériques plutôt qu'analogiques ?

- Quelles limites à l'utilisation des signaux numériques ?

1

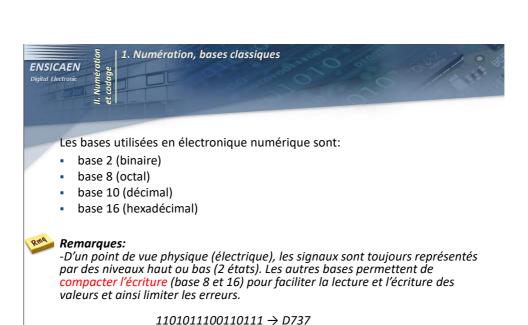

2

- La base 10 facilite l'interfaçage homme-machine (affichage-saisie).

ENSICAEN

Digital Electronic

Solution

1. Numération, bases classiques el popular el

#### Remarques:

- Toute base s'écrit dans son propre système de numération

- Un décalage à gauche un nombre par sa base

- Un décalage à droite un nombre par sa base

**Question :** combien faut-il de chiffres n dans une base B pour représenter un nombre décimal de N chiffre ?

Application numérique: base 2 et N=2.

3

3

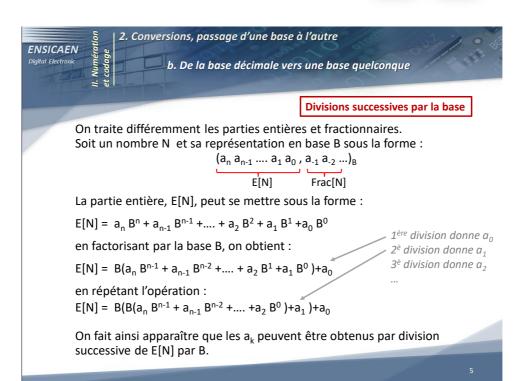

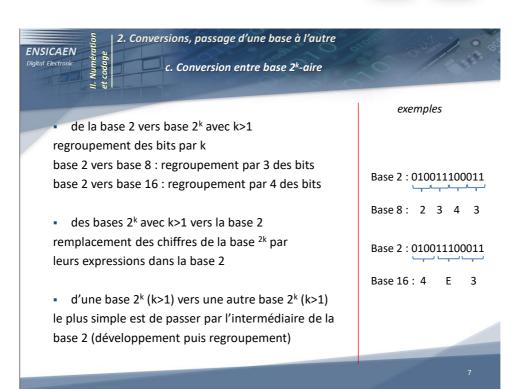

્રુંટ 2. Conversions, passage d'une base à l'autre ENSICAEN રેફ હ

a. D'une base B quelconque à la base décimale

On attribue le poids de chaque chiffre.

Soit un nombre N=  $(a_n a_{n-1} .... a_1 a_0, a_{-1} a_{-2} ...)_B$ alors la valeur en base 10 correspondant est :

$(N)_{10} = a_n B^n + a_{n-1} B^{n-1} + .... a_1 B^1 + a_0 B^0 + a_{-1} B^{-1} + a_{-2} B^{-2} + ....$

Exemples:

5

2. Conversions, passage d'une base à l'autre **ENSICAEN** b. De la base décimale vers une base quelconque Multiplications successives par la base (cont.) La partie fractionnaire, Frac[N], peut se mettre sous la forme : Frac[N] =  $a_{-1} B^{-1} + a_{-2} B^{-2} + .... + a_{-m} B^{-m}$ 1ère multiplication donne a<sub>-1</sub> en multipliant par la base, on obtient : 2è division donne a<sub>-2</sub> 3è division donne a<sub>-3</sub> B.Frac[N] =  $a_{-1} + a_{-2} B^{-1} + .... + a_{-m} B^{-m+1}$ en répétant l'opération :  $B^2$ .Frac[N] =  $B a_{-1} + (a_{-2} + .... + a_{-m} B^{-m+2})$ On fait ainsi apparaître que les a<sub>-k</sub> peuvent être obtenus par multiplications successives par B.

7

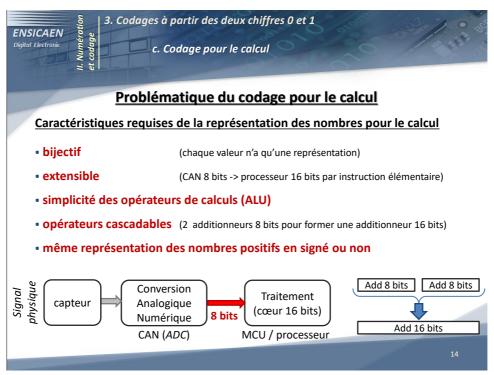

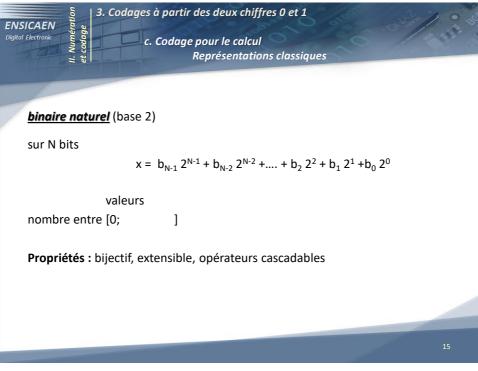

D'un point de vue de l'électronique numérique, les données réellement manipulées sont des **niveaux haut ou bas**, c'est-à-dire des 1 ou des 0 binaires.

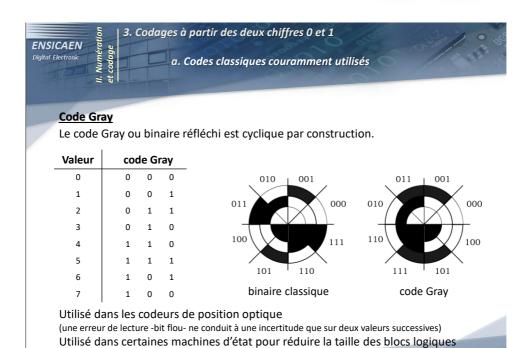

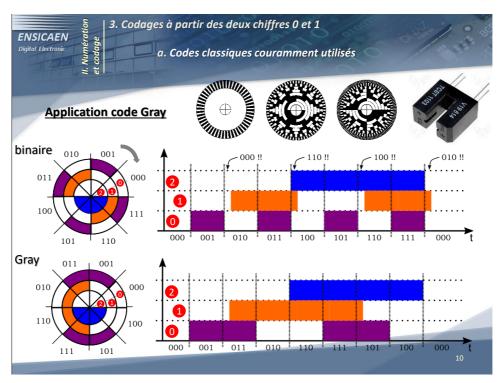

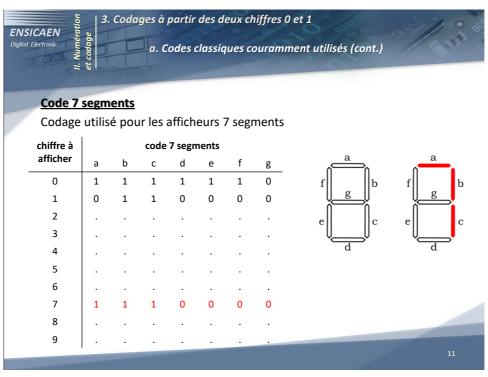

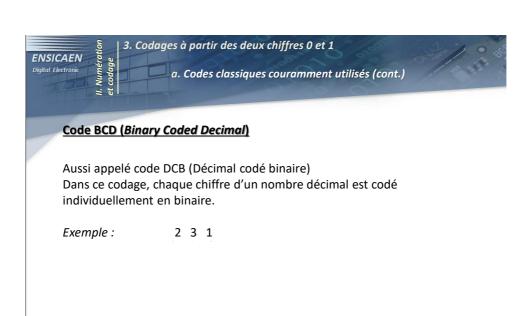

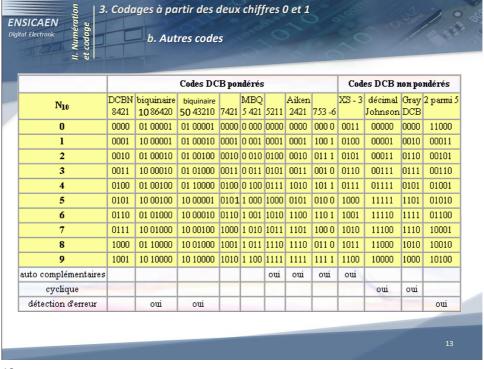

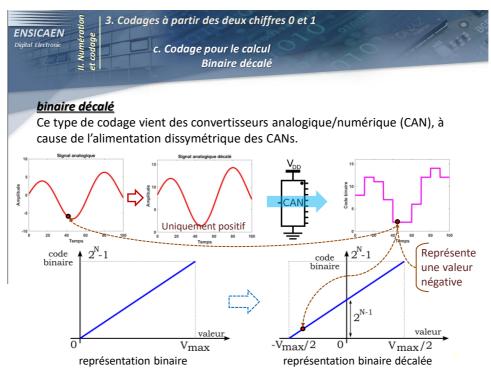

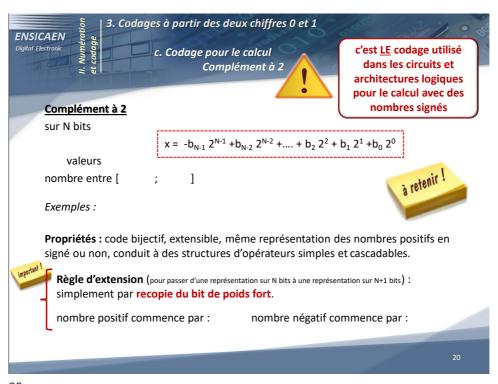

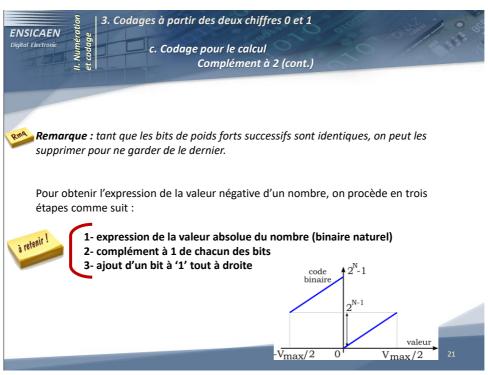

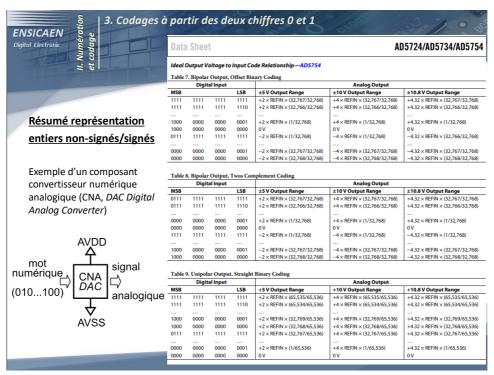

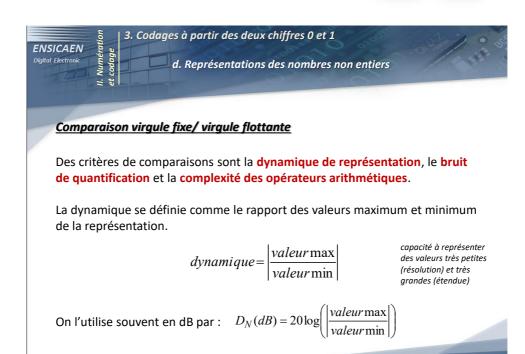

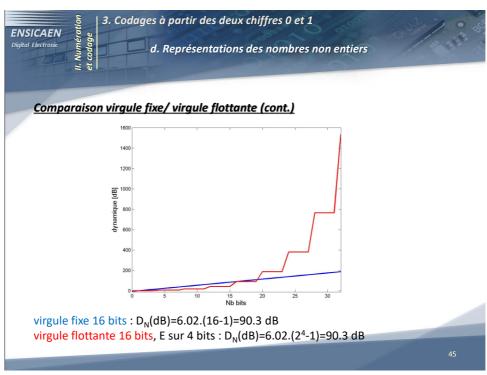

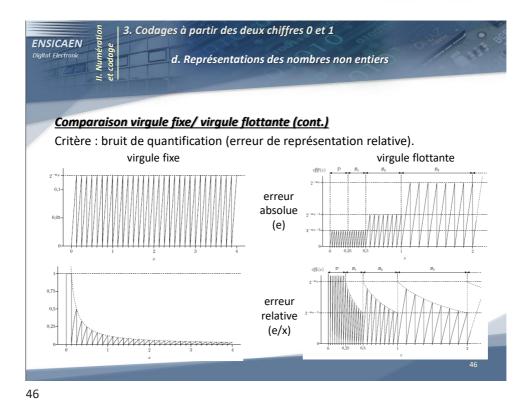

A partir de ces deux chiffres, il existe plusieurs possibilités pour le codage des grandeurs ou signaux. Ces possibilités sont choisies en fonction de leur adéquation à une fonction (affichage, capteur position), de leur précision ou dynamique de représentation ou bien de leur simplicité d'implémentation (réduction de l'électronique associée).

Par la suite, on distinguera les codes pondérés des codes non pondérés.

#### **Définitions:**

un code est pondéré si chaque chiffre est affecté d'un poids.

un code est continu si les mots binaires consécutifs sont adjacents, c'est-à-dire qu'ils ne diffèrent que d'un bit.

un code est cyclique s'il est continu et si le premier et le dernier mots sont adjacents.

9

11

12

**Remarque :** on ne peut pas faire de calcul facilement avec ce code.

13

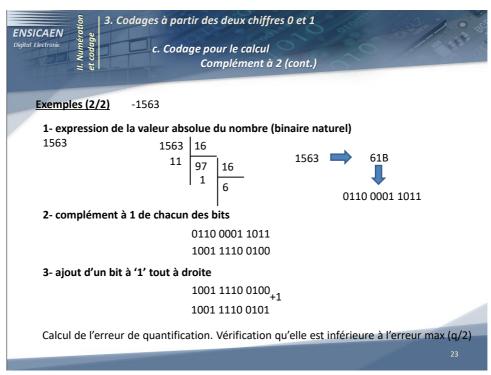

22

24

ENSICAEN

Digital Electronic

To be a bound of the section of the s

Rmq

#### Remarques : décalages arithmétiques et logiques

- un décalage à droite correspond à une division par 2 exemple :

- un décalage à gauche correspond à une multiplication par 2 exemple:

Attention au débordement

Différence entre

LSR (Logic Shift Right) décalage à droite logique (introduction d'un 0) et ASR (Arithmetic Shift Right) (introduction du bit de signe)

Décalages spéciaux sur certains processeurs/microcontrôleurs par exemple PIC18 : décalage circulaire (RRNCF (rotate right f))

26

26

BOUND AND THE PROPERTY OF T

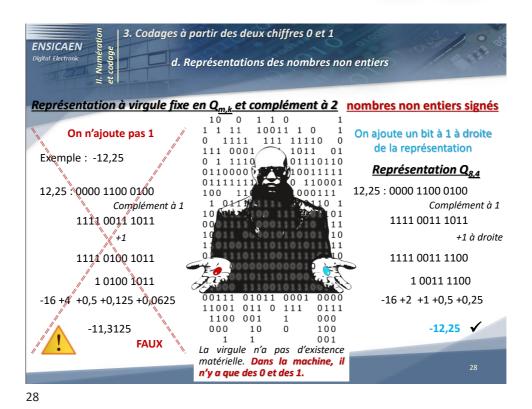

#### Représentation à virgule fixe en Qm,k

Alors la valeur représentée appartient à l'intervalle :

Le quantum (pas de quantification) est :

Remarque: la virgule n'a pas d'existence matérielle. Les opérateurs arithmétiques traitent les nombres à virgule fixe comme des entiers (suite de 0 et de 1).

27

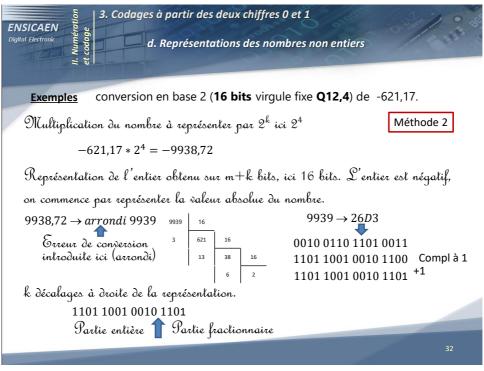

3. Codages à partir des deux chiffres 0 et 1 **ENSICAEN** d. Représentations des nombres non entiers Obtenir la représentation à virgule fixe en Qm k Méthode 1: Méthode 2: Si négatif: représentation de la valeur Multiplication du nombre à absolue puis complément à 2. représenter par 2k. Pour les nbs positifs et la valeur Représentation de l'entier obtenu absolue, obtention de la partie entière sur m+k bits. par divisions successives, obtention de la partie fractionnaire par k décalages à droite de la multiplications successives. représentation.

3. Codages à partir des deux chiffres 0 et 1 ENSICAEN d. Représentations des nombres non entiers conversion en base 2 (16 bits virgule fixe Q12,4) de -621,17. nombre négatif, conversion en 3 étapes Méthode 1 On représente la valeur absolue du nombre soit 621.17 partie fractionnaire mult. succ. partie entière dir. succ. 0,17 621 16 0,72  $621\rightarrow26D_h$  $0,17 \rightarrow 0,2B_h$ x 16 arrondi  $0,17 \rightarrow 0,3h$   $0,17 \rightarrow 0,0011$ 2,72 11,52  $621 \rightarrow 001001101101$ Complément à « 1 » de chacun des bits 0010 0110 1101 0011 1101 1001 0010 1100 +1On ajoute un bit à « 1 » tout à droite 1101 1001 0010 1101 L'erreur est introduite lors de l'arrondi :  $0,0011 \rightarrow 0,1875$ erreur = |0,1875-0,17| = 0,0175 < erreur<sub>max</sub> =  $q/2 = 2^{-5} = 0.03125$

32

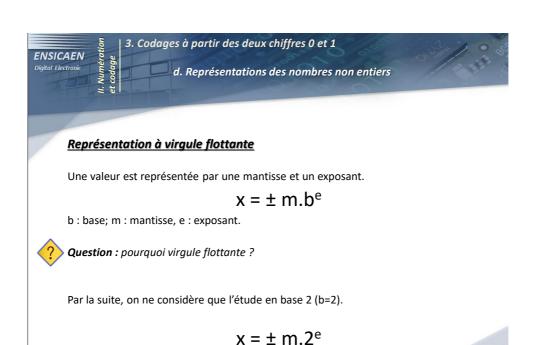

#### Représentation à virgule flottante (cont.)

Avec cette écriture, on peut avoir plusieurs solutions pour représenter une même valeur. Alors, on fixe une contrainte sur la mantisse de façon à avoir une écriture unique pour la valeur.

La mantisse est représentée en virgule fixe. On utilise un bit pour le signe.

Finalement, le nombre en virgule flottante s'écrit :

$$x = (-1)^{S}.1,F.2^{E}$$

Le 1 de la partie entière n'a pas besoin d'être stocké. Il s'agit d'un 1 implicite.

35

35

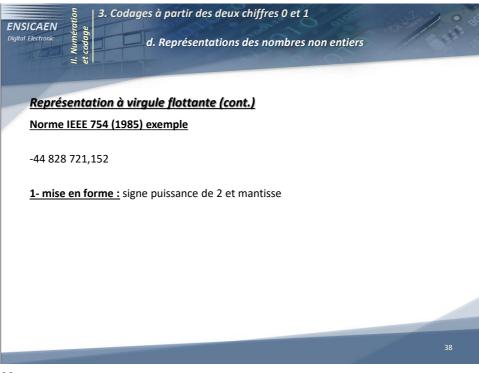

#### Représentation à virgule flottante (cont.)

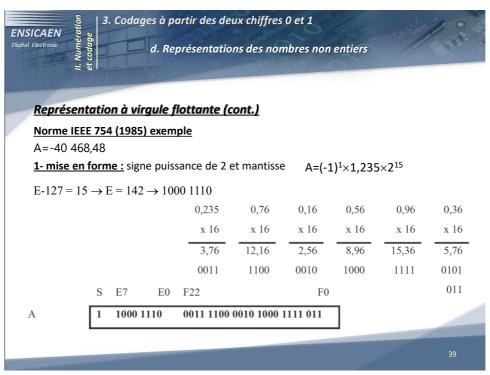

#### Norme IEEE 754 (1985)

C'est la représentation standard pour l'arithmétique en virgule flottante, utilisée par la plupart des systèmes pour améliorer la compatibilité entre les architectures et la portabilité des applications.

$x = (-1)^{S}.1, F.2^{E-B}$

B biais ou décalage 1+mantisse (E≠0)

Exposant biaisé: l'exposant est représenté par un entier auquel on soustrait un biais B.

Exemple de la représentation IEEE 754 sur 32 bits (simple precision) :

exposant E sur 8 bits, F sur 23 bits :  $x = (-1)^S \cdot 1, F \cdot 2^{E-127}$

$$S E_7 E_6 E_5 E_4 E_3 E_2 E_1 E_0 F_{22} F_{21} F_{20} \dots F_2 F_1 F_0$$

Représentation IEEE 754 sur 64 bits (double precision), exposant E sur 11 bits.

38

d. Représentations des nombres non entiers

#### Représentation à virgule flottante (cont.)

#### Norme IEEE 754 (cont.)

Nombres dénormalisés : en plus de la représentation normalisée avec le 1 implicite, la norme définit une représentation alternative lorsque l'exposant vaut 0. Pour représenter les valeurs très prochse de 0.

$$x = (-1)^{S}.0, F.2^{-126}$$

Exposant = 0

Mantisse ≠0

Cette dénormalisation permet de représenter le 0 lorsque F=0.

Valeur la plus petite dénormalisée : 0,0000....01.21-B

Continuité avec normalisé : dénormalisé : 0,11111....111.21-B

(-1)<sup>S</sup>.0,11..11.2<sup>-126</sup> (-1)<sup>S</sup>.1,00..00.2<sup>1-127</sup> normalisé: 1,00000..0000.2<sup>1-B</sup>

Représentations spéciales :

infini : représenté par un exposant maximum et F=0. Le bit de signe distingue +  $\infty$  et - $\infty$ .

NaN: Not a Number, correspondant au résultat de calcul incorrect. Représenté

par un exposant maximal et F non nul.

40

40

#### Représentation à virgule flottante (cont.)

#### Norme IEEE 754 (cont.)

| Exemples : sur 32 bits valeur | S | $E_7E_6E_5E_4E_3E_2E_1E_0$ | F <sub>22</sub> F <sub>21</sub> F <sub>20</sub> F <sub>2</sub> F <sub>1</sub> F <sub>0</sub> |

|-------------------------------|---|----------------------------|----------------------------------------------------------------------------------------------|

| 0                             | 0 | 0000 0000                  | 000000                                                                                       |

| -0                            | 1 | 0000 0000                  | 000000                                                                                       |

| ∞                             | 0 | 1111 1111                  | 000000                                                                                       |

| -∞                            | 1 | 1111 1111                  | 000000                                                                                       |

| NaN                           | 0 | 1111 1111                  | 000100                                                                                       |

| 6,5                           | 0 | 1000 0001                  | 101000                                                                                       |

| 7,347.10 <sup>-39</sup>       | 0 | 0000 0000                  | 101000                                                                                       |

|                               |   |                            |                                                                                              |

42

44

ENSICAEN

Digital Electronic

ENSICAEN

Digital Electronic

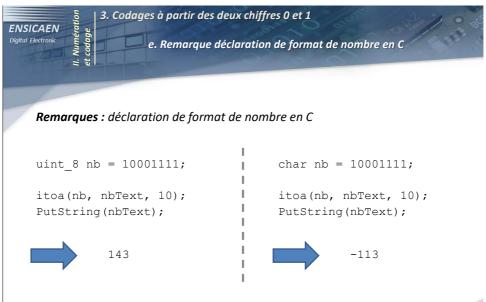

E. Remarque déclaration de format de nombre en C

Rmq

Remarques : déclaration de format de nombre en C

Une déclaration de type de nombre sert à définir :

- la taille (multiple de 8 bits).

- le domaine qui peut varier suivant la nature du type (signé, non signé).

| type                      | taille  | domaine                                        |  |  |  |  |  |

|---------------------------|---------|------------------------------------------------|--|--|--|--|--|

| unsigned char             | 8 bits  | 0 à 255                                        |  |  |  |  |  |

| char                      | 8 bits  | -128 à 127                                     |  |  |  |  |  |

| unsigned int (OS 32 bits) | 32 bits | 0 à 4 294 967 295                              |  |  |  |  |  |

| short int                 | 16 bits | -32768 à 32767                                 |  |  |  |  |  |

| int (OS 32 bits)          | 32 bits | -2 147 483 648 à 2 147 483 647                 |  |  |  |  |  |

| long                      | 32 bits | -2 147 483 648 à 2 147 483 647                 |  |  |  |  |  |

| float                     | 32 bits | 3,4.10 <sup>-38</sup> à 3,4.10 <sup>38</sup>   |  |  |  |  |  |

| double                    | 64 bits | 1,7.10 <sup>-308</sup> à 1,7.10 <sup>308</sup> |  |  |  |  |  |

Même contenu mémoire, interprétation différente

48

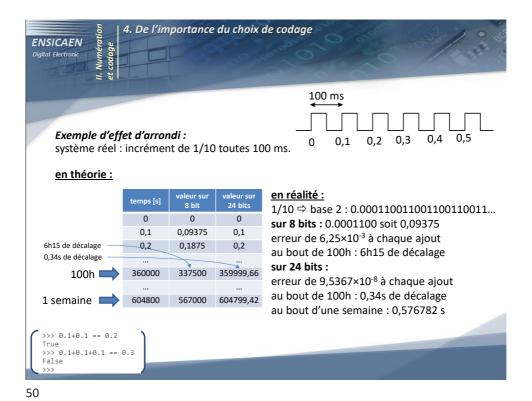

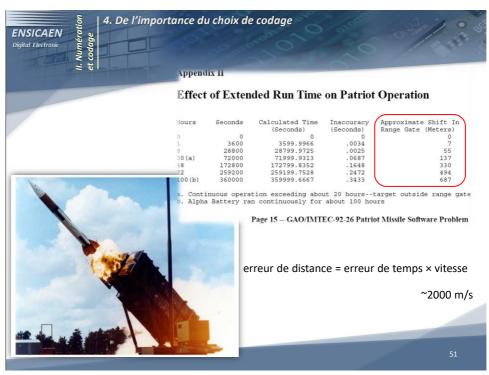

En fonction de la vulnérabilité de l'application : le code doit permettre la représentation des grandeurs manipulées sans débordement (ou avec signalisation du débordement) et avoir une résolution suffisante pour que le bruit de quantification (dit autrement l'arrondi de représentation) n'est pas d'impact sur l'application.

Le compromis est à trouver entre le nombre de bits utilisés pour la représentation et la dynamique associée et la taille/consommation/coût de l'unité de calcul associée.

$$3+2,19 =$$

- Comment est représentée physiquement la virgule du codage à virgule fixe au cœur des circuits numériques ?

- Pourquoi impose-t-on une contrainte à la valeur de la mantisse dans le cas du codage en virgule flottante ?

- Quels sont les avantages/inconvénients relatifs des codages en virgule fixe et virgule flottante ?

5

1

ENSICAEN

Digital Electronic

Digi

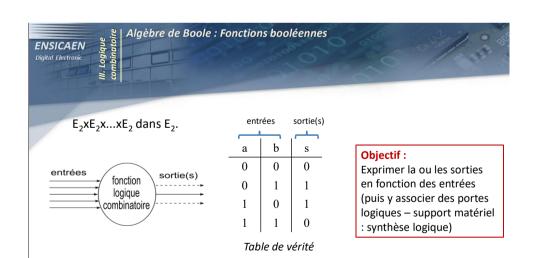

- Algèbre de Boole définie sur E<sub>2</sub> constitué des éléments {0,1}

- Trois opérations de base :

|   | complén | nentation | union + max OU |   |   | intersection · min ET |   |   |

|---|---------|-----------|----------------|---|---|-----------------------|---|---|

| Ì | а       | ā         | а              | b | S | а                     | b | S |

|   | 0       | 1         | 0              | 0 | 0 | 0                     | 0 | 0 |

|   | 1       | 0         | 0              | 1 | 1 | 0                     | 1 | 0 |

|   |         |           | 1              | 0 | 1 | 1                     | 0 | 0 |

|   |         |           | 1              | 1 | 1 | 1                     | 1 | 1 |

- 0 : élément neutre de l'union, élément minimum.

- 1 : élément neutre de l'intersection, élément maximum.

Algèbre de Boole : Propriétés des opérations de base ENSICAEN

$\forall a,b,c \in E_2$

$a.\bar{a}=0$  complémentation :  $a + \bar{a} = 1$

a,b=b,a commutativité : a + b = b + a

(a.b).c = a.(b.c) associativité : (a + b) + c = a + (b + c)

a.(b + c) = a.b + a.c distributivité : a + (b.c) = (a + b).(a + c)

5

Algèbre de Boole : Théorèmes associés à l'algèbre de Boole

ENSICAEN

$\forall a,b,c \in E_2$

a.a = aidempotence a + a = a

a + a.b = aabsorption:  $a.\left(a+b\right)=a$

involution:  $\bar{\bar{a}} = a$

Théorème de Morgan :  $\overline{a+b} = \overline{a}.\overline{b}$  ;  $\overline{a.b} = \overline{a} + \overline{b}$

Théorème de Shannon :  $a + b = a, b + a, \bar{b} + \bar{a}, b$

$a + \bar{a} \cdot b = a + b$ Consensus de 1<sup>ière</sup> espèce:  $a.(\bar{a}+b)=a.b$

Consensus de 2<sup>nd</sup> espèce :  $a.b + \overline{b}.c = a.b + \overline{b}.c + a.c$

b variable biforme  $(a+b).(\overline{b}+c)=(a+b).(\overline{b}+c).(a+c)$

Termes de Consensus

Introduire le terme de Consensus de 2<sup>nd</sup> espèce s'il permet de réduire l'expression par absorption,

Exemple :

F = fēb + hgfēdca + hgb

absorption,

absorption,

$F = f\bar{e}b + hgf\bar{e}dca + hg\bar{b} + hgf\bar{e}$

retirer le terme de consensus.

Absorption

retrait Consensus

$F = f\bar{e}b + hg\bar{b}$

7

Deux façons d'exprimer une fonction booléenne :

- la forme somme de produit ou disjonctive normale ΣΠ

- la forme produit de somme ou conjonctive normale ΠΣ

Idée: avoir l'expression la plus compacte possible

Moins de support physique, moins de consommation, plus rapide

Algèbre de Boole : Forme somme de produit ΣΠ

- Première forme canonique

- On associe une variable binaire m<sub>i</sub> à chaque entrée de la table

- minterm , terme produit

$m_0$  est associé à la ligne 0, actif/vrai (à 1) pour la ligne 0  $m_0=1$  si a=0 et b=0 c'est-à-dire si  $\bar a=1$  et  $\bar b=1$   $m_0=\bar a.\, \bar b$

| m <sub>i</sub> | a | b | s              |

|----------------|---|---|----------------|

| $m_0$          | 0 | 0 | $s_0$          |

| $\mathbf{m}_1$ | 0 | 1 | $\mathbf{s}_1$ |

| $m_2$          | 1 | 0 | $s_2$          |

| $m_3$          | 1 | 1 | $s_3$          |

$m_0 = \overline{a}.\overline{b}$ ;  $m_1 = \overline{a}.b$ ;  $m_2 = a.\overline{b}$ ;  $m_3 = a.b$

$$s = s_0 m_0 + s_1 m_1 + s_2 m_2 + s_3 m_3$$

9

9

Algèbre de Boole : Forme somme de produit ΣΠ (cont.)

- Simplification de l'expression

- minterm pour lesquels la fonction vaut 1

- Dans le cas de la fonction XOR

$$s = m_1 + m_2$$

$$s = \bar{a}.b + a.\bar{b}$$

Rmq

Remarque: réalisation simple avec des portes NAND

🧵 🙎 | Algèbre de Boole : Forme produit de somme ΠΣ

ENSICAEN

Digital Electronic

- Seconde forme canonique

- On associe une variable binaire M<sub>i</sub> à chaque entrée de la table

- maxterm, terme somme

| $M_{i}$        | a | b | S         |

|----------------|---|---|-----------|

| $M_0$          | 0 | 0 | $0 (s_0)$ |

| $\mathbf{M}_1$ | 0 | 1 | $1 (s_1)$ |

| $M_2$          | 1 | 0 | $1 (s_2)$ |

| $M_{2}$        | 1 | 1 | $0 (s_2)$ |

| • | Exemple | pour la | fonction | XOR |

|---|---------|---------|----------|-----|

|---|---------|---------|----------|-----|

|   | a | b | $M_0$ | $M_1$ | $M_2$ | $M_3$ |

|---|---|---|-------|-------|-------|-------|

|   | 0 | 0 | 0     | 1     | 1     | 1     |

|   | 0 | 1 | 1     | 0     | 1     | 1     |

|   | 1 | 0 | 1     | 1     | 0     | 1     |

| • | 1 | 1 | 1     | 1     | 1     | 0     |

$$M_0 = a + b$$

;  $M_1 = a + \overline{b}$ ;  $M_2 = \overline{a} + b$ ;  $M_3 = \overline{a} + \overline{b}$

$$s = (s_0 + M_0).(s_1 + M_1).(s_2 + M_2).(s_3 + M_3)$$

Maxterm constitué de l'union (OU) de toutes les variables d'entrée, non complémentées si leur valeur est 0, complémentées si leur valeur est 1.

11

11

့ နို့ | Algèbre de Boole : Forme produit de somme ΠΣ (cont.)

- ENSICAEN

Digital Electronic

- Simplification de l'expression

- On conserve les maxterm pour lesquels la fonction vaut 0

| a | b | $M_0$ | $M_1$ | $M_2$ | $M_3$ | $M_0M_3$ | s |

|---|---|-------|-------|-------|-------|----------|---|

| 0 | 0 | 0     | 1     | 1     | 1     | 0        | 0 |

| 0 | 1 | 1     | 0     | 1     | 1     | 1        | 1 |

| 1 | 0 | 1     | 1     | 0     | 1     | 1        | 1 |

| 1 | 1 | 1     | 1     | 1     | 0     | 0        | 0 |

$$_{S}$$

=  $0$  si  $M_{\,0}$ =  $0$  ou si  $M_{\,3}$ =  $0$  c'est-à-dire si  $M_{0}.M_{3}=0$

$$s=M_0.M_3 \hspace{1cm} s=(a+b).(\bar{a}+\bar{b})$$

Remarque : réalisation simple avec des portes NOR

1.

13

16

18

28

32

Sortie d'un circuit logique

Types de sortie (étage de sortie): la sortie d'un circuit logique peut être fournie soit par 2 transistors complémentaires « totem-pole » ou par un seul transistor « collecteur ouvert ».

La sortie totem-pole est pratique pour cascader des circuits de même technologie, même alimentation.

La sortie collecteur ouvert est pratique pour changer de niveau de tension ou la réalisation d'un ET câblé (bus I2C).

Sortance : capacité d'une porte logique à servir de source à d'autres portes logiques. Courant de sortie > somme de courant d'entrée des portes en aval. En CMOS limite de vitesse de fonctionnement.

Court-circuit (état indéterminé)

A = 1

B = 0

V = 'X'

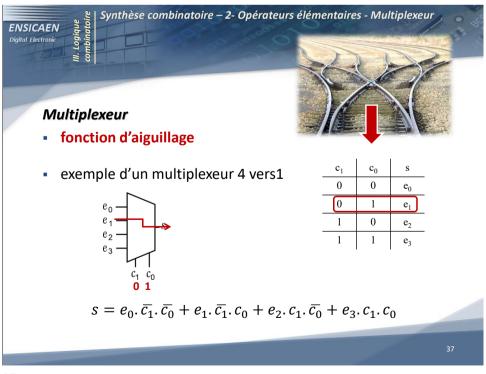

Synthèse combinatoire - 2- Opérateurs élémentaires - Démultiplexeur

#### Démultiplexeur

opérateur dual

$$s_0 = \overline{c_1}.\overline{c_0}.e$$

$$s_1 = \overline{c_1}.c_0.e$$

$$s_2 = c_1.\overline{c_2}.e$$

39

Synthèse combinatoire - 2- Opérateurs élémentaires - Décodeur ENSICAEN

#### Décodeur

- active une sortie parmi 2<sup>N</sup> grâce à N signaux de commande.

- utilisé pour « adresser ».

- équivalent du démultiplexeur avec une entrée de donnée à « 1 »

- exemple de décodeur 4 sorties

$$s_0 = \overline{c_1}.\overline{c_0}$$

$$\mathbf{s}_1 = \overline{\mathbf{c}_1}.\mathbf{c}_0$$

$$\mathbf{s}_2 = \mathbf{c}_1.\overline{\mathbf{c}_0}$$

$$s_3 = c_1.c_0$$

| $\mathbf{c}_1$ | $c_0$ | $s_0$ | $\mathbf{s}_1$ | $s_2$ | $s_3$ |

|----------------|-------|-------|----------------|-------|-------|

| 0              | 0     | 1     | 0              | 0     | 0     |

| 0              | 1     | 0     | 1              | 0     | 0     |

| 1              | 0     | 0     | 0              | 1     | 0     |

| 1              | 1     | 0     | 0              | 0     | 1     |

Dans certains décodeurs discrets, la sortie active peut être au niveau bas et les inactives au niveau haut.

45

49

54

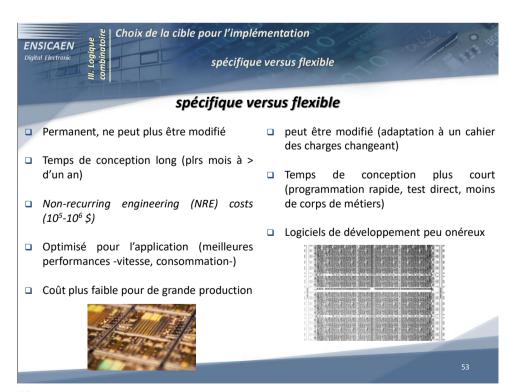

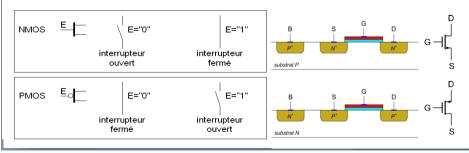

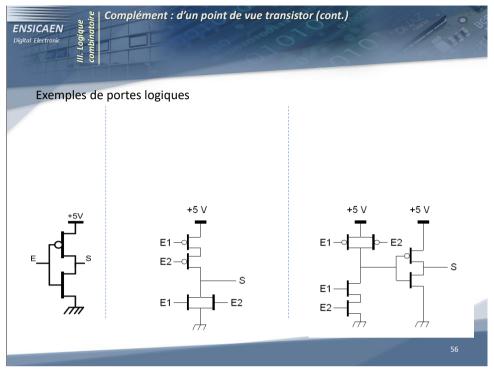

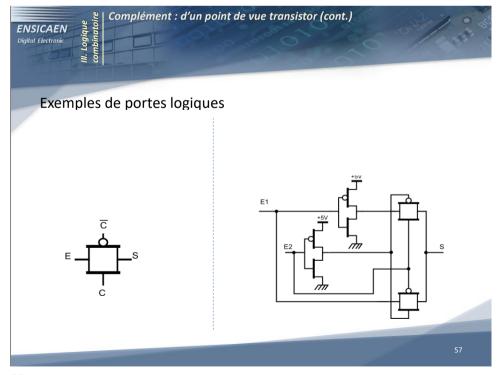

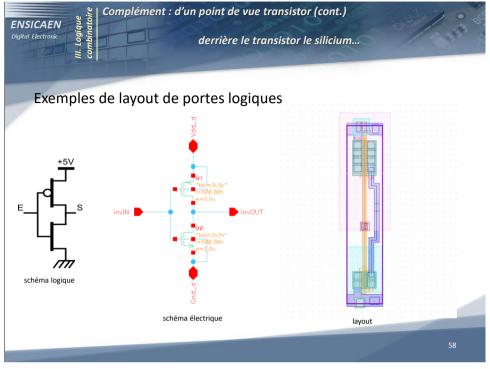

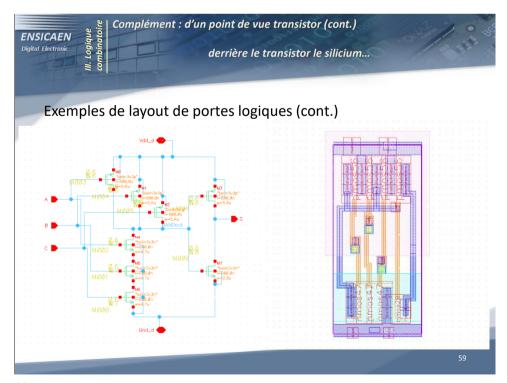

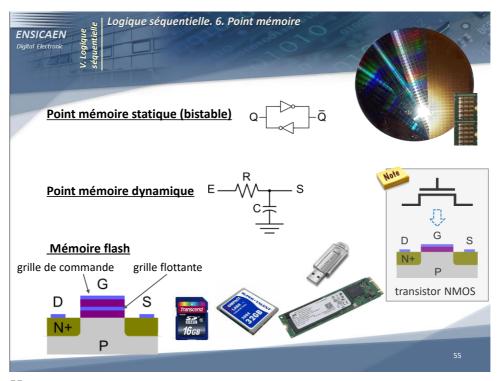

D'un point de vue physique, les portes logiques sont réalisées à partir de transistors. Plusieurs types de transistors peuvent être employés, mais le plus couramment utilisé est celui des transistors Métal Oxyde Isolant plus connu sous le sigle transistor MOS. La fabrication des portes logiques s'appuie alors sur l'utilisation de deux types de transistors : les transistors NMOS et les transistors PMOS. Ces transistors sont utilisés comme des interrupteurs et chacun de ces transistors est caractérisé par les niveaux logiques qui le rendent assimilable à un interrupteur ouvert ou bien fermé.

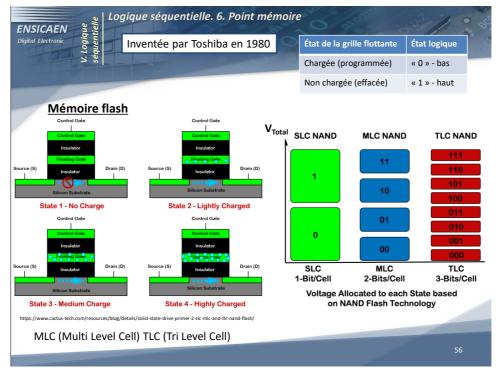

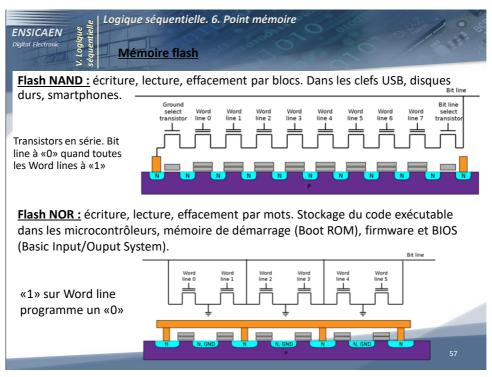

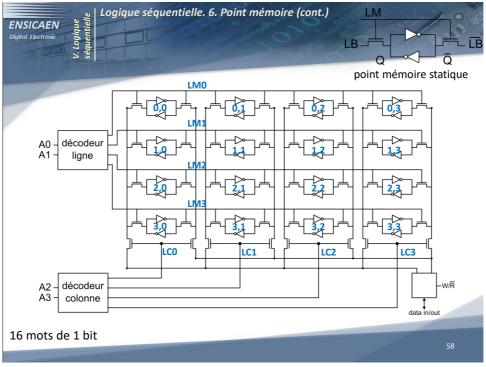

56

58

1

3

5

6

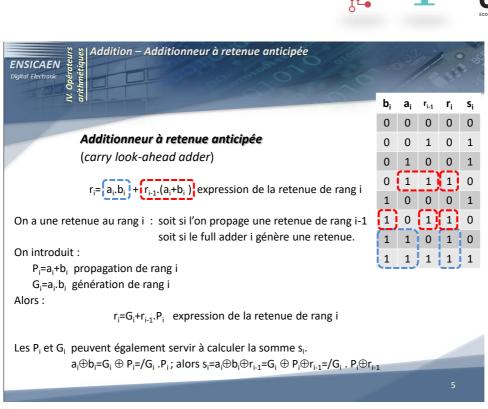

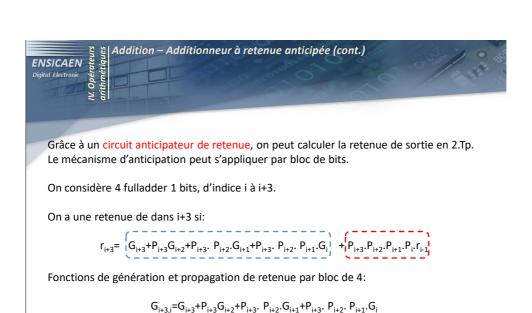

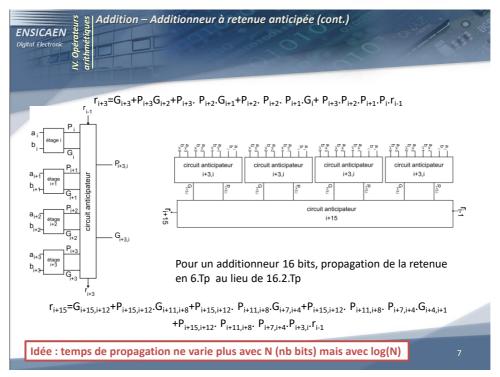

$P_{i+3,i} = P_{i+3}.P_{i+2}.P_{i+1}.P_{i}$

$r_{i+3} = G_{i+3,i} + P_{i+3,i} \cdot r_{i-1}$

9

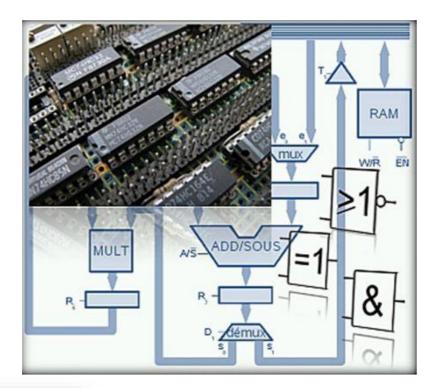

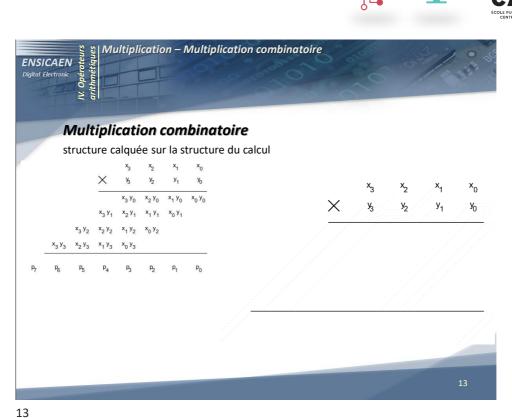

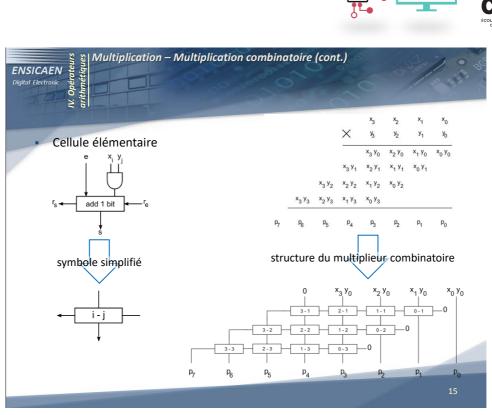

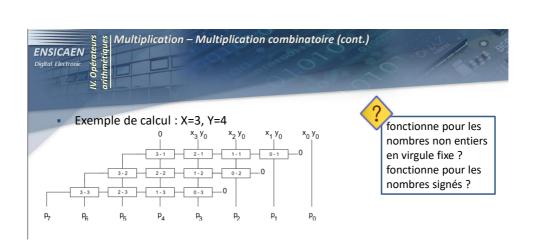

sa Multiplication – Multiplication combinatoire (cont.) ENSICAEN  $[r_1 p_1]=x_1y_0+x_0y_1$ Fait intervenir 2 types d'opérations élémentaires : des produits de bits  $p_1 = x_1 y_0 \oplus x_0 y_1$ des additions de sommes partielles  $r_1 = (x_1y_0).(x_0y_1)$  $[r_2p_2] = x_2y_0 + x_1y_1 + r_1 + x_0y_2$ y<sub>1</sub>  $x_3 y_0$ x<sub>2</sub> y<sub>0</sub> x<sub>1</sub> y<sub>0</sub>  $x_0 y_0$ x<sub>2</sub> y<sub>1</sub> x3 y1 x<sub>0</sub> y<sub>1</sub>  $x_3^{y_2} y_2^{y_2}$ x<sub>1</sub> y<sub>2</sub>  $x_0^{y_2}$ x<sub>1</sub> y<sub>3</sub>  $x_2 y_3$  $x_0 y_3$ - cellule élémentaire dédiée à ces opérations

#

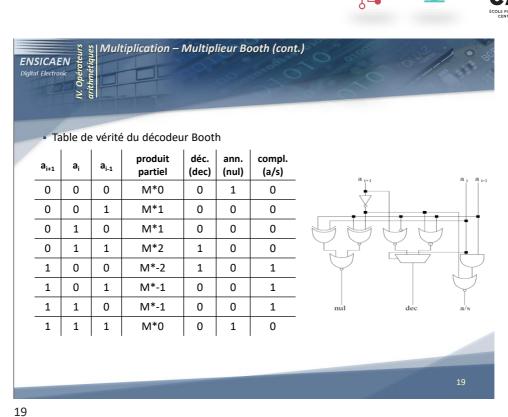

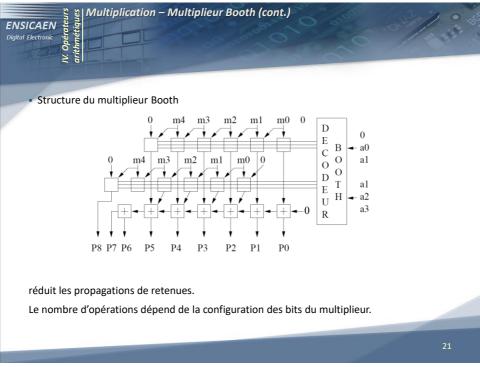

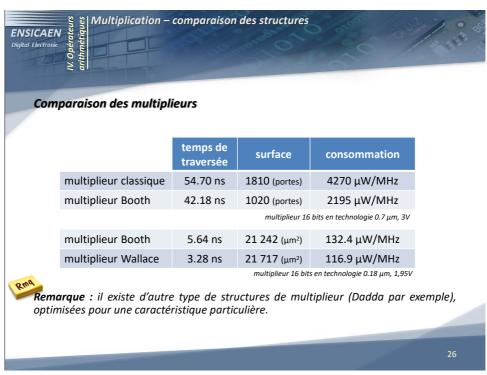

#### **Multiplieur Booth**

Repose sur l'algorithme de Booth, largement utilisé pour les multiplications, qui permet de réduire de moitié le nombre de sommes partielles tout en conservant une structure régulière.

#### Algorithme de Booth:

soit A l'opérande de multiplication : A =  $-a_{N-1} 2^{N-1} + a_{N-2} 2^{N-2} + .... + a_2 2^2 + a_1 2^1 + a_0 2^0$

en utilisant les relations :  $2^i - 2^{i-1} = 2^{i-1}$  et  $2^i = 2^{i+1} - 2 \cdot 2^{i-1}$

on peut écrire :

A =

$$(-2.a_{N-1} + a_{N-2} + a_{N-3})2^{N-2} + (-2.a_{N-3} + a_{N-4} + a_{N-5})2^{N-4} + ...$$

+  $(-2.a_3 + a_2 + a_1)2^2 + (-2.a_1 + a_0 + 0)2^0$

Il s'agit d'une décomposition de Booth d'ordre 2.

17

17

$$A = \left( \frac{2.a_{N-1} + a_{N-2} + a_{N-3}}{2.a_{N-1} + a_{N-2} + a_{N-3}} \right) 2^{N-2} + \left( -2.a_{N-3} + a_{N-4} + a_{N-5} \right) 2^{N-4} + \dots$$

$$+ \left( -2.a_3 + a_2 + a_1 \right) 2^2 + \left( -2.a_1 + a_0 + 0 \right) 2^0$$

Quand un nombre M est multiplié par A, les produits partiels obtenus sont du type :

Le calcul du produit final résulte de la conjugaison de 3 types de commandes :

- complémentation à 2 (\*-1),

- décalage à gauche (\*2),

- annulation (\*0).

Multiplieur Booth constitué d'un décodeur Booth et de cellules élémentaires capables d'exécuter les 3 types de commande.

Idée : multiplication transformée en étapes logiques élémentaires (complémentation, décalage, annulation)

18

Multiplication – Multiplieur Booth (cont.) ENSICAEN Table de vérité d'une cellule élémentaire m i dec a/s carry in nul déc. ann. compl. retenue sortie (dec) (nul) (a/s) (carry out) 0 0 0 m<sub>i</sub>⊕carry<sub>in</sub> m<sub>i</sub>.carry<sub>in</sub> 0 0 1 -m<sub>i</sub>⊕carry<sub>in</sub> -m<sub>i</sub>.carry<sub>in</sub> 0 0 1 1 0 0  $m_{i-1} \oplus carry_{in}$ m<sub>i-1</sub>.carry<sub>in</sub> 1 0 1 -m<sub>i-1</sub>⊕carry<sub>in</sub> -m<sub>i-1</sub>.carry<sub>in</sub> sortie carry out

21

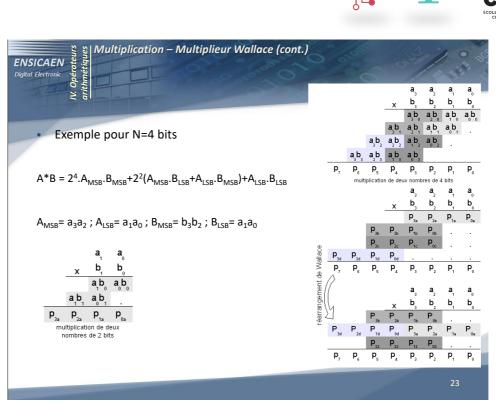

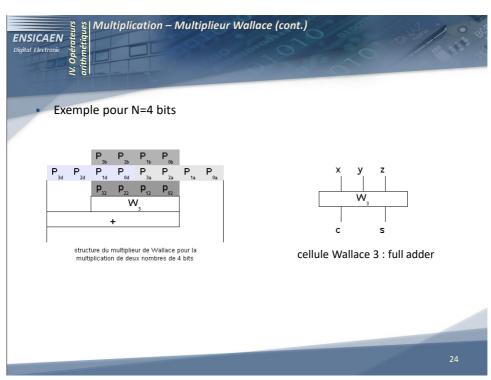

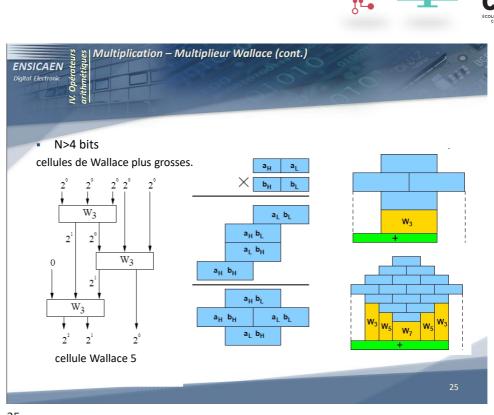

### **Multiplieur Wallace**

Le multiplieur de Wallace n'a pas une structure régulière mais une structure arborescente.

Il repose sur une décomposition de la multiplication en sous-multiplications sur un nombre réduit de bits et sur la combinaison rapide des produits partiels.

Soit A et B sur N bits les nombres à multiplier. On peut écrire :

$$\mathsf{A}^*\mathsf{B} = \mathsf{2}^{\mathsf{N}}.\mathsf{A}_{\mathsf{MSB}}.\mathsf{B}_{\mathsf{MSB}} + \mathsf{2}^{\mathsf{N}/2}(\mathsf{A}_{\mathsf{MSB}}.\mathsf{B}_{\mathsf{LSB}} + \mathsf{A}_{\mathsf{LSB}}.\mathsf{B}_{\mathsf{MSB}}) + \mathsf{A}_{\mathsf{LSB}}.\mathsf{B}_{\mathsf{LSB}}$$

Soit 4 multiplications partielles sur 2 fois moins de bits.

Idée : décomposition en sous-multiplications moins lourdes

2:

23

25

Opérateurs arithmétiques - Remarques générales - Erreurs de calculs ENSICAEN Sources d'erreur de calcul possibles résolution liée au format des données (troncature, arrondi, erreur de représentation) уз У2 y<sub>1</sub>  $y_0$ s<sub>0</sub> addition/soustraction: s<sub>1</sub> - débordement (overflow) y<sub>2</sub> multiplication:  $\mathbf{x}_{2} \, \mathbf{y}_{0}$ x<sub>1</sub> y<sub>0</sub> - arrondi/quantification  $x_3 y_2$ x2 y2  $x_2^y_3$

29

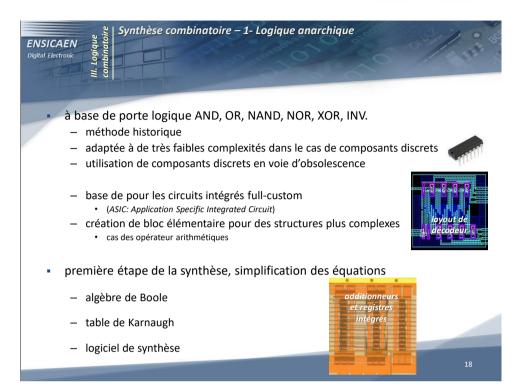

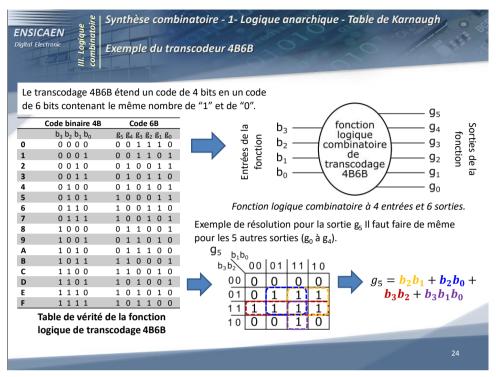

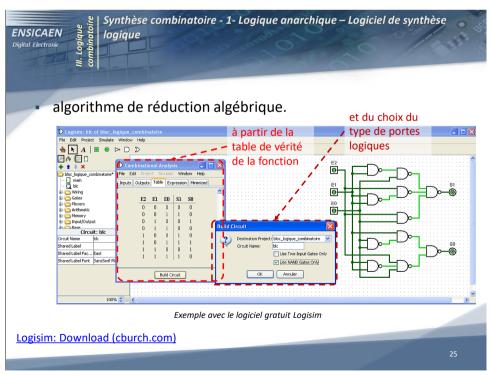

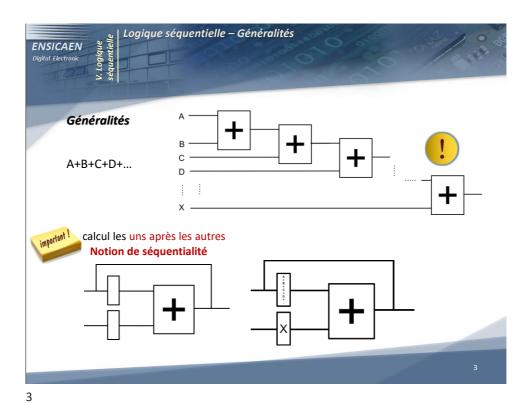

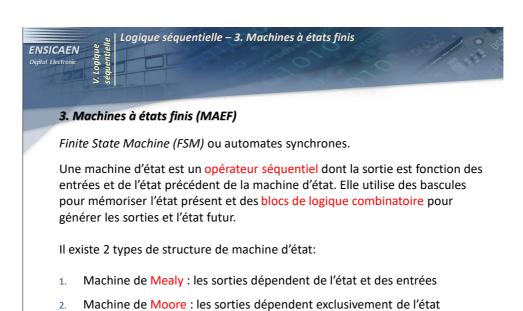

Rappel : Une **fonction logique combinatoire** est une fonction qui prend un ou plusieurs bits d'entrée en entrée et produit un ou plusieurs bits de sortie en sortie. Les sorties de fonctions logiques combinatoires **ne dépendent que des valeurs actuelles des bits d'entrée** et ne tiennent pas compte de l'historique des entrées ou des sorties contrairement aux sorties des fonctions logiques séquentielles.

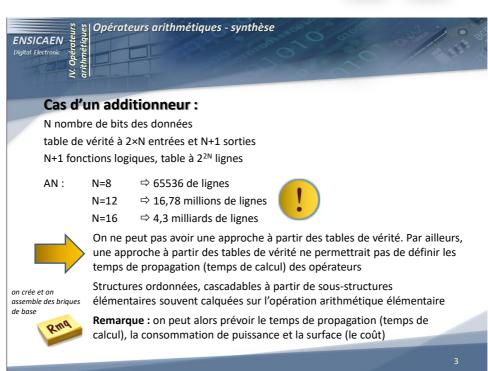

La logique combinatoire est utilisée par exemple pour les **transcodeurs** (passage d'un code à un autre), le **routage** de données (multiplexeur, démultiplexeur) ou les **opérateurs arithmétiques** (additionneur, soustracteur, multiplieur). La synthèse d'un bloc logique combinatoire se fait à partir d'une table de vérité exprimant les sorties de la fonction logique en fonction des entrées.

\_

# ENSICAEN Digital Electronic Orginal Electronic Orginal Sectronic O

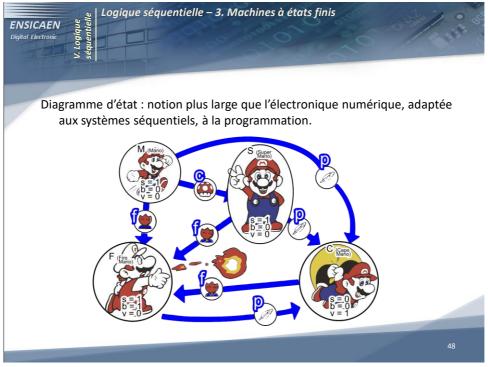

Les portes logiques combinatoires n'ont pas de « mémoire », la valeur de leurs sorties ne dépend que de l'état des entrées.

Ces portes adaptées au décodage ou aux opérations arithmétiques ne permettent pas seule de décrire un système dont l'état évolue.

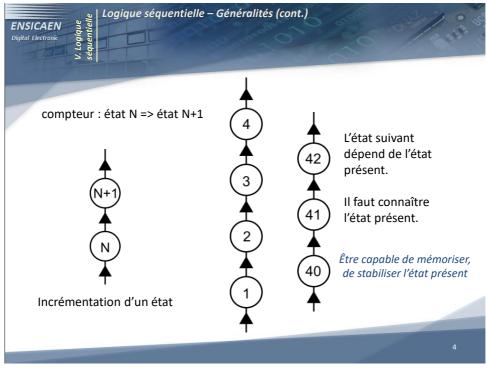

#### Un état : une configuration possible du système.

Exemples:

| lampe           | allumée, éteinte, cassée                      |  |  |  |

|-----------------|-----------------------------------------------|--|--|--|

| feu tricolore   | rouge, vert, orange clignotant, hors service  |  |  |  |

| ordinateur      | allumé, en veille, en veille prolongé, éteint |  |  |  |

| machine à laver | prélavage, lavage, rinçage, essorage, arrêt   |  |  |  |

| compteur        | 0, 1, 2, 3,, N                                |  |  |  |

| smartphone      | verrouillé, déverrouillé                      |  |  |  |

des événements font évoluer le système (passage d'un état à un autre). Exemples : signaux logiques activés (capteurs, boutons), durée écoulée (Timer)

-' /

5

#### Fonction logique combinatoire :

entrée interrupteur / sortie ampoule La valeur de la sortie ne dépend que de la valeur de l'entrée.

#### Fonction logique séquentielle :

entrée interrupteur / sortie feu piéton La valeur de la sortie dépend de l'état du système et de l'entrée.

Idée : en logique séquentielle, le système se souvient que l'on a appuyé et sait dans quel été il est.

ENSICAEN an bigory X Signal Electronic Signal El

Besoin d'un autre type de structures logiques :

portes logiques séquentielles  $\rightarrow$  bascules points mémoires

#### 1. Bascules

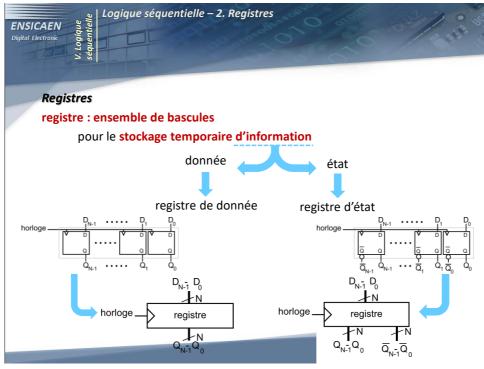

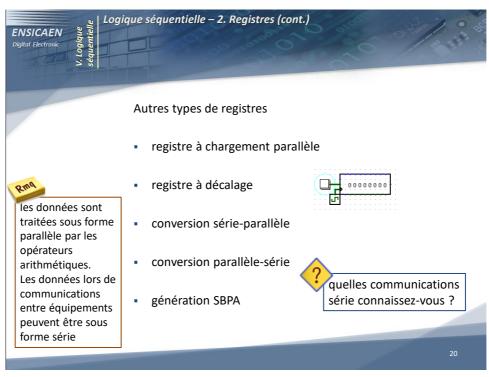

Réalisées à partir de portes logiques élémentaires (ensembles de transistors). Eléments fondamentaux permettant de mémoriser et de modifier l'information.

Utilisées pour le stockage temporaire de données et la réalisation d'automates pour le contrôle de l'évolution des systèmes.

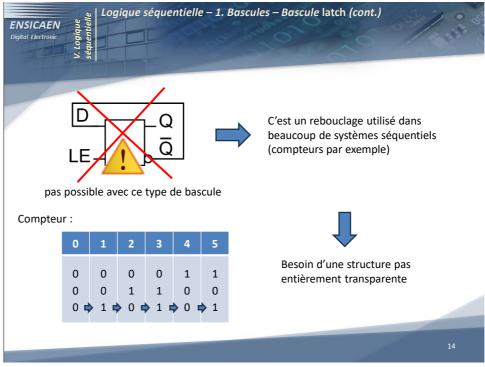

Remarque: les compteurs sont un cas particulier d'automate.

7

7

#### 1. Bascules

Opérateurs élémentaires de mémorisation.

Leur état dépend de celui de leurs entrées mais également de leur état précédent.

état(i+1) = f(état(i), entrées)

(verrouillé + touche écran => déverrouillé)

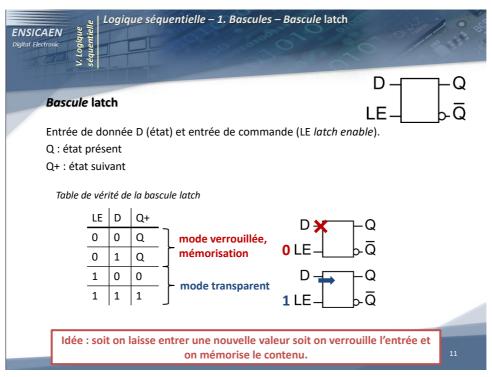

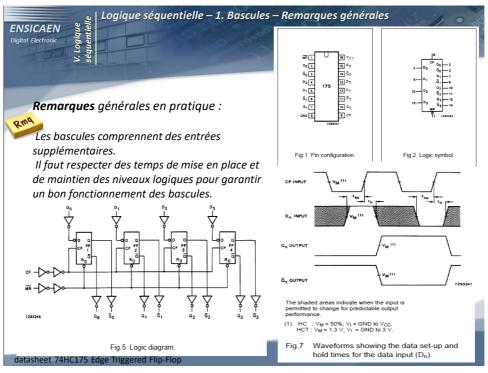

On distingue les bascules asynchrones sensibles au niveau des entrées et les bascules synchrones sensibles au front d'un signal spécial cadençant le système (typiquement un signal d'horloge).

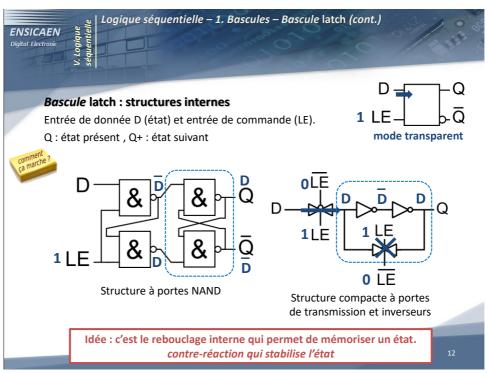

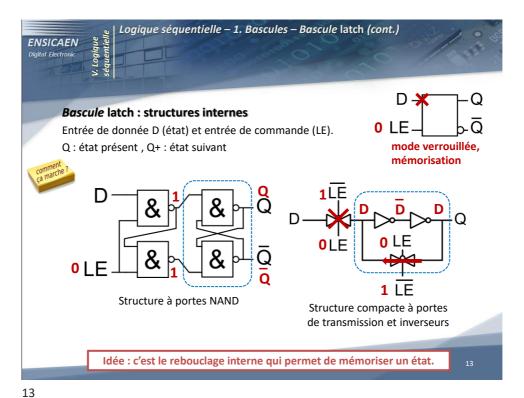

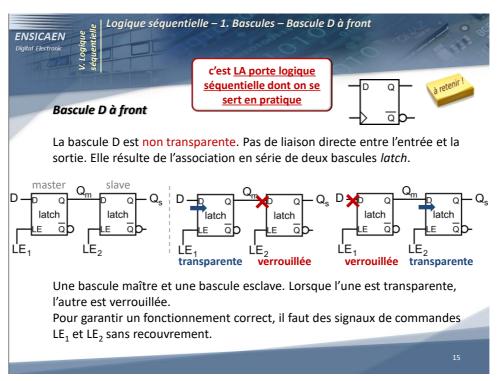

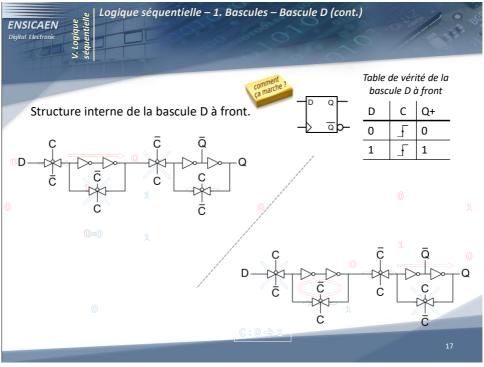

Historiquement : bascules RS, bascules JK. A l'heure actuelle uniquement des bascules synchrones, les bascules D à front constituées de 2 bascules *latch* en série.

20

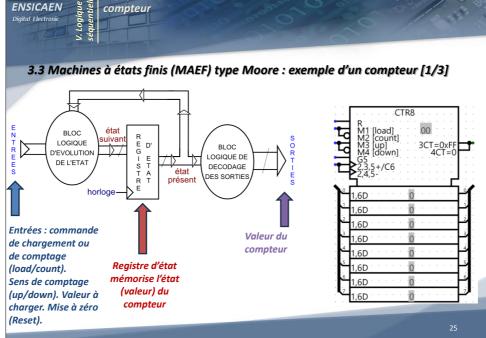

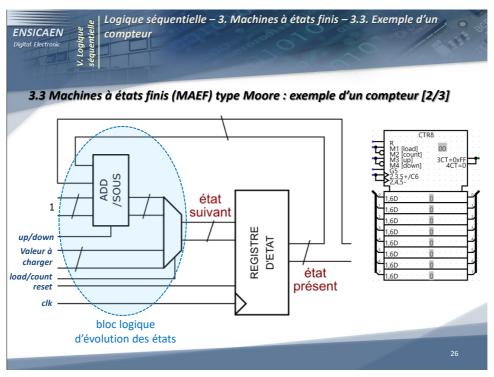

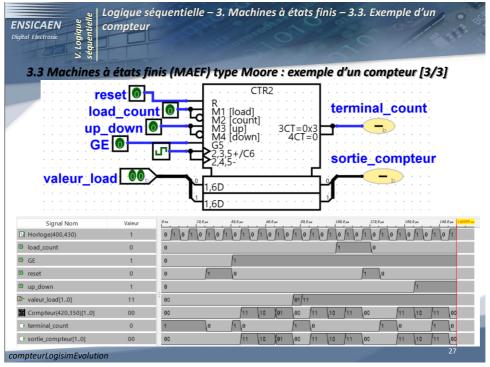

Remarque : les compteurs sont un cas particulier de machine à états finis.

Logique séquentielle – 3. Machines à états finis – 3.3. Exemple d'un

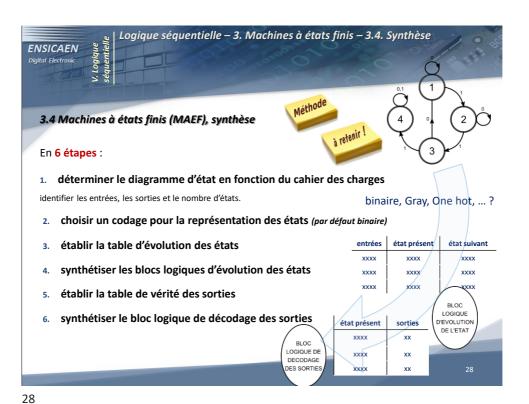

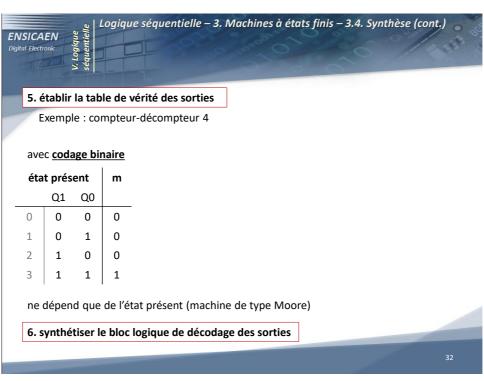

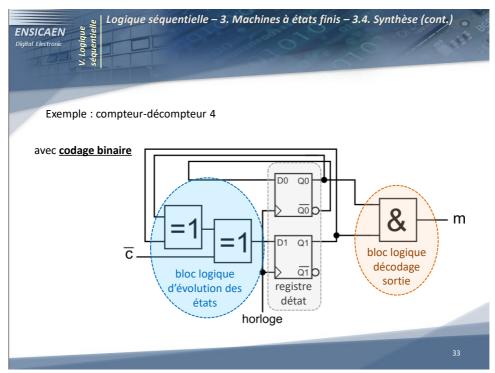

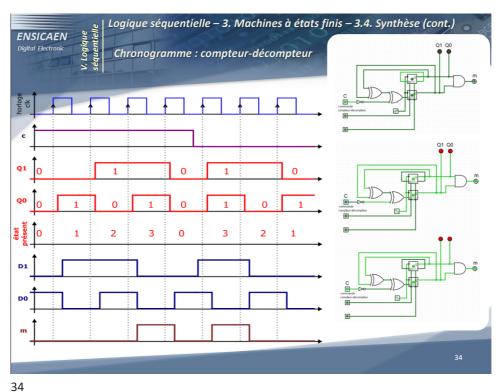

Logique séquentielle - 3. Machines à états finis - 3.4. Synthèse (cont.) **ENSICAEN** Exemple: compteur-décompteur 4, avec m actif pour la valeur maximum 2. choix d'un codage pour les états 1. diagramme d'états ici exemple avec binaire, Gray, one hot une entrée c, une sortie m, 4 états C état présent état suivant 1 0 1 0 XXXX XXXX 2 1 1 XXXX XXXX 2 3 1 XXXX XXXX 3 1 3 0 XXXX XXXX 0 3 0 XXXX XXXX 0 1 XXXX XXXX 2 0 1 XXXX XXXX 0 3 2 XXXX XXXX c=1: comptage c=0: décomptage

| SICA<br>I Elect | NEN<br>ronic | V. Logique<br>séquentielle | Logiqu | ie séq      | uentie  | elle – 3     | Machines à états finis – 3.4. Synthèse (cont. |

|-----------------|--------------|----------------------------|--------|-------------|---------|--------------|-----------------------------------------------|

| 3. ét           |              |                            | e ďévo | olutio      | n des   | états        | 000                                           |

| E               | xempl        | le : co                    | mpteu  | r-déco      | ompte   | ur 4         |                                               |

| tab             | le d'év      | olutio                     | on ave | <u>coda</u> | ge bir  | <u>iaire</u> |                                               |

| С               | éta          | t prés                     | ent    | éta         | it suiv | ant          |                                               |

|                 |              | Q1                         | Q0     |             | D1      | D0           |                                               |

| 1               | 0            | 0                          | 0      | 1           | 0       | 1            |                                               |

| 1               | 1            | 0                          | 1      | 2           | 1       | 0            |                                               |

| 1               | 2            | 1                          | 0      | 3           | 1       | 1            |                                               |

| 1               | 3            | 1                          | 1      | 0           | 0       | 0            |                                               |

| 0               | 0            | 0                          | 0      | 3           | 1       | 1            |                                               |

| 0               | 1            | 0                          | 1      | 0           | 0       | 0            |                                               |

|                 | 2            | 1                          | 0      | 1           | 0       | 1            |                                               |

| 0               | _            |                            |        |             | !       |              |                                               |

30

| SICA    | EN     | que<br>itielle             | Logiqu  | ie sėgi     | uentie | elle – 3    |

|---------|--------|----------------------------|---------|-------------|--------|-------------|

| Electro | onic   | V. Logique<br>séquentielle |         |             |        |             |

| syn     | thétis | er le k                    | oloc lo | gique       | d'évo  | lution      |

| E       | xempl  | e : co                     | mpteu   | r-déco      | mpte   | ur 4        |

| tabl    | e d'év | olutio                     | n ave   | <u>coda</u> | ge bir | <u>aire</u> |

| С       | éta    | t prés                     | ent     | éta         | t suiv | ant         |

|         |        | Q1                         | Q0      |             | D1     | D0          |

| 1       | 0      | 0                          | 0       | 1           | 0      | 1           |

| 1       | 1      | 0                          | 1       | 2           | 1      | 0           |

| 1       | 2      | 1                          | 0       | 3           | 1      | 1           |

| 1       | 3      | 1                          | 1       | 0           | 0      | 0           |

| 0       | 0      | 0                          | 0       | 3           | 1      | 1           |

| 0       | 1      | 0                          | 1       | 0           | 0      | 0           |

| 0       | 2      | 1                          | 0       | 1           | 0      | 1           |

| 0       | 3      | 1                          | 1       | 2           | 1      | 0           |

| ,       |        |                            |         |             |        |             |

ENSICAEN

Digital Electronic

Digital Electronic

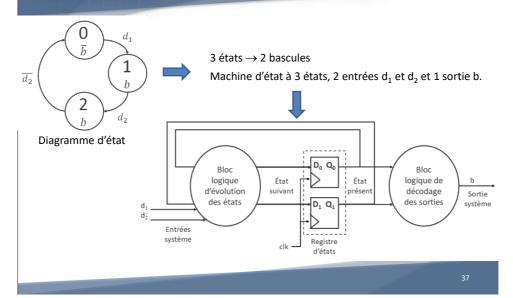

Exemple synthèse 2 [1/3]

Logique séquentielle – 3. Machines à états finis – 3.4. Synthèse (cont.)

Exemple synthèse 2 [2/3]

#### Table de vérité du bloc logique d'évolution des états

|                |                | entrées        |            | sorties       |               |                |                |

|----------------|----------------|----------------|------------|---------------|---------------|----------------|----------------|

| 1              | rées<br>èmes   | É              | tat préser | nt            | État suivant  |                |                |

| d <sub>1</sub> | d <sub>2</sub> | Q <sub>1</sub> | $Q_0$      | État<br>prés. | État<br>suiv. | D <sub>1</sub> | D <sub>0</sub> |

| 0              | х              | 0              | 0          | 0             | 0             | 0              | 0              |

| 1              | х              | 0              | 0          | 0             | 1             | 0              | 1              |

| Х              | 0              | 0              | 1          | 1             | 1             | 0              | 1              |

| Х              | 1              | 0              | 1          | 1             | 2             | 1              | 0              |

| Х              | 1              | 1              | 0          | 2             | 2             | 1              | 0              |

| Х              | 0              | 1              | 0          | 2             | 0             | 0              | 0              |

| Х              | х              | 1              | 1          | 3             | 0*            | 0              | 0              |

<sup>\*</sup>Intérêt à renvoyer vers un cycle du système, sinon reste planté. Mais cela dépend des applications et cahiers des charges.

Table de Karnaugh pour D<sub>1</sub>

| 00 | 01    | 11                | 10                      |

|----|-------|-------------------|-------------------------|

| 0  | 0     | 0                 | 0                       |

| 0  | 1     | 0                 | 1                       |

| 0  | 1     | 0                 | 1                       |

| 0  | 0     | 0                 | 0                       |

|    | 0 0 0 | 0 0<br>0 1<br>0 1 | 0 0 0<br>0 1 0<br>0 1 0 |

#### Table de Karnaugh pour Do

| ( | $Q_1Q_0$       |    |    |    |    |

|---|----------------|----|----|----|----|

| 1 | $Q_1Q_0$ $d_2$ | 00 | 01 | 11 | 10 |

|   | 00             | 0  | 0  | 0  | 0  |

|   | 01             | 0  | 0  | 0  | 0  |

|   | 11             | 1  | 1  | 0  | 0  |

|   | 10             | 1  | 1  | 0  | 0  |

30

38

ENSICAEN

**ENSICAEN**

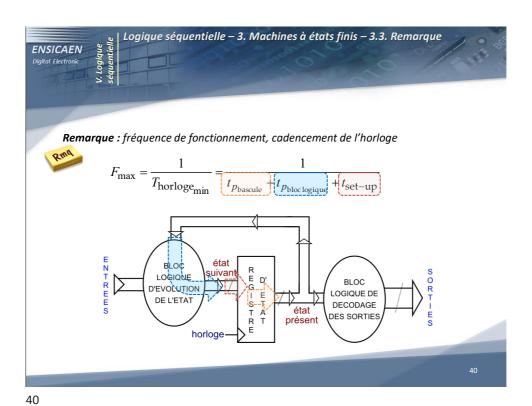

Logique séquentielle – 3. Machines à états finis – 3.4. Synthèse (cont.)

Exemple synthèse 2 [3/3]

Les tables de Karnaugh ne permettent pas de grande simplification dans ce cas.

$$D_1 = d_2 \cdot (Q_1 \oplus Q_0)$$

$$D_0 = d_1 \cdot \overline{Q_1} \cdot \overline{Q_0} + \overline{d_2} \cdot \overline{Q_1} \cdot Q_0$$

Table de vérité du bloc logique de décodage des sorties

| Ét<br>(enti | sortie |      |   |  |  |  |  |  |

|-------------|--------|------|---|--|--|--|--|--|

| $Q_1$       | $Q_0$  | état | b |  |  |  |  |  |

| 0           | 0      | 0    | 0 |  |  |  |  |  |

| 0           | 1      | 1    | 1 |  |  |  |  |  |

| 1           | 0      | 2    | 1 |  |  |  |  |  |

| 1           | 1      | 3    | Х |  |  |  |  |  |

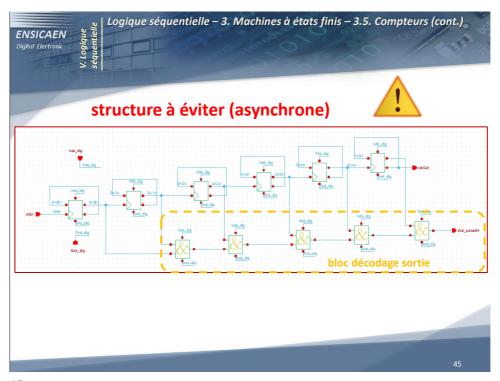

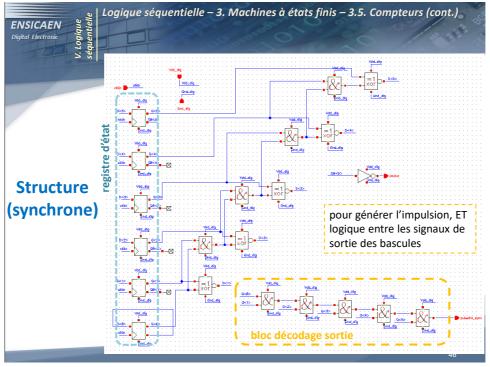

Structure à éviter

Les signaux de sortie des bascules de cette structure ne sont pas synchrones. On ne peut pas s'en servir pour générer des signaux à cause des aléas (états transitoires non souhaités).

Exemple : on souhaite générer une impulsion toutes les 64 périodes (fin de comptage (cf Timer 0 du PIC18)).

#### Compteurs/décompteurs à préchargement

- · Compteur programme

- Timer (signal de fin de comptage/décomptage, IT)

#### <u>Séquenceur</u>

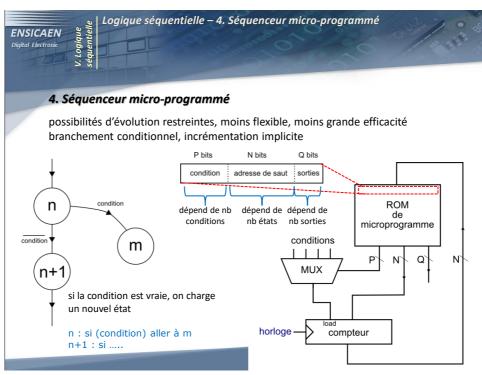

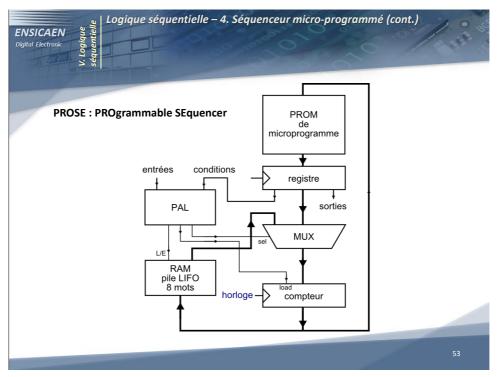

Les machines à états finis sont une des structures pour réaliser des séquenceurs (automates) dans les cœurs de calculateur.

L'autre structure est le séquenceur micro-programmé.

49

49

Le séquenceur coordonne les sous-opérations nécessaires pour l'exécution des instructions.

#### solution câblée:

l'automate du séquenceur est une machine à états finis câblée. privilégiée pour les processeurs RISC (Reduced Instruction Set Core/Computer ); exemple PIC

#### solution micro-programmée:

l'automate est un séquenceur micro-programmé (microprogramme contenu dans une ROM)

privilégiée pour les processeurs CISC (Complex Instruction Set Computer)

Quelle différence essentielle existe-t-il entre un système asynchrone et un système synchrone ?

Quels sont les avantages/inconvénients respectifs des systèmes asynchrones et synchrones ?

De quel type sont la grande majorité des microprocesseurs et microcontrôleurs (synchrone ou asynchrone) ?

50

59

Quels sont les deux types de machine à états finis ?

Quelles sont les étapes de la synthèse d'une machine à états finis ?

Quels sont les avantages/inconvénients relatifs des solutions machine à états finis et séquenceur microprogrammé pour la synthèse de circuits logiques séquentiels ?

1

Architecture ENSICAEN PIC18 Timer 0 Sync with Internal Clocks TMR0I High Byte T0CKI pin T0SE T0CS Read TMR0L T0PS2:T0PS0 PSA TMR0H fréquence d'horloge configurable Internal Data Bus registres de préchargement

5